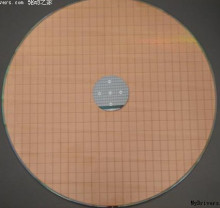

晶圆指制造半导体晶体管或集成电路的衬底(也叫基片)。由于是晶体材料,其形状为圆形,所以称为晶圆。衬底材料有硅、锗、GaAs、InP、GaN等。由于硅最为常用,如果没有特别指明晶体材料,通常指硅晶圆。1

在硅晶片上可加工制作成各种电路元件结构,而成为有特定电性功能的集成电路产品。晶圆的原始材料是硅,而地壳表面有用之不竭的二氧化硅。二氧化硅矿石经由电弧炉提炼,盐酸氯化,并经蒸馏后,制成了高纯度的多晶硅,其纯度高达99.999999999%。2

制造过程

单晶硅棒的直径是由籽晶拉出的速度和旋转速度决定的,一般来说,上拉速率越慢,生长的单晶硅棒直径越大。而切出的晶圆片的厚度与直径有关,虽然半导体器件的制备只在晶圆的顶部几微米的范围内完成,但是晶圆的厚度一般要达到1 mm,才能保证足够的机械应力支撑,因此晶圆的厚度会随直径的增长而增长。1

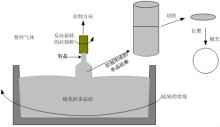

晶圆制造厂把这些多晶硅融解,再在融液里种入籽晶,然后将其慢慢拉出,以形成圆柱状的单晶硅晶棒,由于硅晶棒是由一颗晶面取向确定的籽晶在熔融态的硅原料中逐渐生成,此过程称为“长晶”。硅晶棒再经过切段,滚磨,切片,倒角,抛光,激光刻,包装后,即成为集成电路工厂的基本原料——硅晶圆片,这就是“晶圆”。1

化学气相沉积化学气相沉积是在制造微电子器件时被用来沉积出某种薄膜的技术,这种薄膜可能是介电材料或者半导体。物理气相沉积技术则是使用惰性气体,撞击溅镀靶材,在晶圆表面沉积出所需的材质。制程反应室内的高温和真空环境可以使这些金属原子结成晶粒,在经过图案化(patterned)和蚀刻,得到所需的导电电路。2

光学显影光学显影是将光罩上的图形转换到薄膜上。光学显影一般包括光阻涂布、烘烤、光照对准、曝光和显影等步骤。干式蚀刻是最常用的蚀刻方式,其以气体为主要的蚀刻媒介,由电浆来驱动反应。蚀刻是将表面某种不需要的材质部分移除。2

化学机械研磨化学机械研磨(Chemical Mechanical Polishing,CMP)是既有机械研磨又有酸碱溶液式的化学研磨两种相结合的技术,可以使晶圆表面较为平坦,方便后面工序。在进行研磨时,研磨浆在晶圆和研磨垫之间。影响 CMP 的因素有:研磨头的压力和晶圆平坦度,旋转速度,研磨浆的化学成分等等。2

基本原料

硅是由石英砂所精练出来的,晶圆便是硅元素加以纯化(99.999%),接着是将这些纯硅制成硅晶棒,成为制造集成电路的石英半导体的材料,经过照相制版,研磨,抛光,切片等程序,将多晶硅融解拉出单晶硅晶棒,然后切割成一片一片薄薄的晶圆。硅片广泛用于集成电路(IC)基板、半导体封装衬底材料,硅片划切质量直接影响芯片的良品率及制造成本。硅片划片方法主要有金刚石砂轮划片、激光划片。激光划片是利用高能激光束聚焦产生的高温使照射局部范围内的硅材料瞬间气化,完成硅片分离,但高温会使切缝周围产生热应力,导致硅片边缘崩裂,且只适合薄晶圆的划片。超薄金刚石砂轮划片,由于划切产生的切削力小,且划切成本低,是应用最广泛的划片工艺。由于硅片的脆硬特性,划片过程容易产生崩边、微裂纹、分层等缺陷,直接影响硅片的机械性能。同时,由于硅片硬度高、韧性低、导热系数低,划片过程产生的摩擦热难于快速传导出去,易造成刀片中的金刚石颗粒碳化及热破裂,使刀具磨损严重,严重影响划切质量。1

制造工艺表面清洗晶圆表面附着大约2μm的Al2O3和甘油混合液保护层,在制作前必须进行化学刻蚀和表面清洗。1

初次氧化由热氧化法生成SiO2 缓冲层,用来减小后续中Si3N4对晶圆的应力氧化技术:干法氧化Si(固)+O2 à SiO2(固)和湿法氧化Si(固)+2H2O à SiO2(固)+2H2。干法氧化通常用来形成,栅极二氧化硅膜,要求薄,界面能级和固定

热CVD

热处理在涂敷光刻胶之前,将洗净的基片表面涂上附着性增强剂或将基片放在惰性气体中进行热处理。这样处理是为了增加光刻胶与基片间的粘附能力,防止显影时光刻胶图形的脱落以及防止湿法腐蚀时产生侧面腐蚀(sideetching)。光刻胶的涂敷是用转速和旋转时间可自由设定的甩胶机来进行的。首先、用真空吸引法将基片吸在甩胶机的吸盘上,把具有一定粘度的光刻胶滴在基片的表面,然后以设定的转速和时间甩胶。由于离心力的作用,光刻胶在基片表面均匀地展开,多余的光刻胶被甩掉,获得一定厚度的光刻胶膜,光刻胶的膜厚是由光刻胶的粘度和甩胶的转速来控制。所谓光刻胶,是对光、电子束或X线等敏感,具有在显影液中溶解性的性质,同时具有耐腐蚀性的材料。一般说来,正型胶的分辨率高,而负型胶具有感光度以及和下层的粘接性能好等特点。光刻工艺精细图形(分辨率,清晰度),以及与其他层的图形有多高的位置吻合精度(套刻精度)来决定,因此有良好的光刻胶,还要有好的曝光系统。3

晶圆的背面研磨工艺晶圆的集成电路制造,为了降低器件热阻、提高工作散热及冷却能力、便于封装,在硅晶圆正面制作完集成电路后,需要进行背面减薄。晶圆的背面研磨工艺,是在晶圆的正面贴一层膜保护已经制作好的集成电路,然后通过研磨机来进行减薄。晶圆背面研磨减薄后,表面会形成一层损伤层,且翘曲度高,容易破片。为了解决这些问题,需要对晶圆背面进行湿法硅腐蚀,去除损伤层,释放晶圆应力,减小翘曲度及使表面粗糙化。使用槽式的湿法机台腐蚀时,晶圆正面及背面均与腐蚀液接触,正面贴的膜必须耐腐蚀,从而保护正面的集成电路。使用单片作业的湿法机台,晶圆的正面通常已被机台保护起来,不会与腐蚀液或者腐蚀性的气体有接触,可以撕膜后再进行腐蚀。4

除氮化硅此处用干法氧化法将氮化硅去除。4

离子注入离子布植将硼离子 (B+3) 透过 SiO2 膜注入衬底,形成P型阱离子注入法是利用电场加速杂质离子,将其注入硅衬底中的方法。离子注入法的特点是可以精密

退火处理去除光刻胶放高温炉中进行退火处理 以消除晶圆中晶格缺陷和内应力,以恢复晶格的完整性。使植入的掺杂原子扩散到替代位置,产生电特性。2

去除氮化硅层用热磷酸去除氮化硅层,掺杂磷 (P+5) 离子,形成 N 型阱,并使原先的SiO2 膜厚度增加,达到阻止下一步中n 型杂质注入P 型阱中。1

去除SIO2层退火处理,然后用 HF 去除 SiO2 层。4

干法氧化法干法氧化法生成一层SiO2 层,然后LPCVD 沉积一层氮化硅。此时P 阱的表面因SiO2 层的生长与刻蚀已低于N 阱的表面水平面。这里的SiO2 层和氮化硅的作用与前面一样。接下来的步骤是为了隔离区和栅极与晶面之间的隔离层。3

光刻技术和离子刻蚀技术利用光刻技术和离子刻蚀技术,保留下栅隔离层上面的氮化硅层。3

湿法氧化生长未有氮化硅保护的 SiO2 层,形成 PN 之间的隔离区。3

生成SIO2薄膜热磷酸去除氮化硅,然后用 HF 溶液去除栅隔离层位置的 SiO2 ,并重新生成品质更好的 SiO2 薄膜 , 作为栅极氧化层。3

氧化LPCVD 沉积多晶硅层,然后涂敷光阻进行光刻,以及等离子蚀刻技术,栅极结构,并氧化生成 SiO2 保护层。3

形成源漏极表面涂敷光阻,去除 P 阱区的光阻,注入砷 (As) 离子,形成 NMOS 的源漏极。用同样的方法,在 N 阱区,注入 B 离子形成 PMOS 的源漏极。3

沉积利用 PECVD 沉积一层无掺杂氧化层,保护元件,并进行退火处理。3

沉积掺杂硼磷的氧化层含有硼磷杂质的SiO2 层,有较低的熔点,硼磷氧化层(BPSG) 加热到800 oC 时会软化并有流动特性,可使晶圆表面初级平坦化。3

深处理

(1)薄膜的沉积方法根据其用途的不同而不同,厚度通常小于 1um 。有绝缘膜、半导体薄膜、金属薄膜等各种各样的薄膜。薄膜的沉积法主要有利用化学反应的CVD(chemical vapor deposition) 法以及物理现象的PVD(physical vapor deposition) 法两大类。CVD 法有外延生长法、HCVD , PECVD 等。PVD 有溅射法和真空蒸发法。一般而言, PVD 温度低,没有毒气问题; CVD 温度高,需达到1000 oC 以上将气体解离,来产生化学作用。PVD 沉积到材料表面的附着力较CVD 差一些, PVD 适用于在光电产业,而半导体制程中的金属导电膜大多使用PVD 来沉积,而其他绝缘膜则大多数采用要求较严谨的CVD 技术。以PVD 被覆硬质薄膜具有高强度,耐腐蚀等特点。3

(2)真空蒸发法( Evaporation Deposition )采用电阻加热或感应加热或者电子束等加热法将原料蒸发淀积到基片上的一种常用的成膜方法。蒸发原料的分子(或原子)的平均自由程长( 10 -4 Pa 以下,达几十米),所以在真空中几乎不与其他分子碰撞可直接到达基片。到达基片的原料分子不具有表面移动的能量,立即凝结在基片的表面,所以,在具有台阶的表面上以真空蒸发法淀积薄膜时,一般,表面被覆性(覆盖程度)是不理想的。但若可将Crambo真空抽至超高真空(

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国