NPN晶体管是晶体管的一种,当基极b点电位高于发射极e点电位零点几伏时,发射结处于正偏状态,而集电极C点电位高于b点电位几伏时,集电结处于反偏状态,集电极电源Ec要高于基极电源Ebo。

简介NPN型晶体管,由三块半导体构成,其中两块N型和一块P型半导体组成,P型半导体在中间,两块N型半导体在两侧。NPN型晶体管是电子电路中最重要的器件之一,它最主要的功能是电流放大和开关作用1。

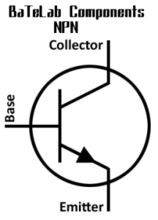

NPN型晶体管的电路符号

制造工艺设计1.首先在ATHENA中定义0.8um*1.0um的硅区域作为基底,掺杂为均匀的砷杂质,浓度为2.0e16/cm3,然后在基底上注入能量为18ev,浓度为4.5e15/cm3的掺杂杂质硼,退火,淀积一层厚度为0.3um的多晶硅,淀积过后,马上进行多晶硅掺杂,掺杂为能量50ev,浓度7.5e15/cm3的砷杂质,接着进行多晶硅栅的刻蚀(刻蚀位置在0.2um处)此时形成N++型杂质(发射区)。刻蚀后进行多晶氧化,由于氧化是在一个图形化(即非平面)以及没有损伤的多晶上进行的,所以使用的模型将会是fermi以及compress,进行氧化工艺步骤时分别在干氧和氮的气氛下进行退火,接着进行离子注入,注入能量18ev,浓度2.5e13/cm3的杂质硼,随后进行侧墙氧化层淀积并进行刻蚀,再一次注入硼,能量30ev,浓度1.0e15/cm3,形成P+杂质(基区)并作一次镜像处理即可形成完整NPN结构,最后淀积铝电极2。

2.三次注入硼的目的

第一次硼注入形成本征基区;第二次硼注入自对准(self-aligned)于多晶硅发射区以形成一个连接本征基区和 p+ 基极接触的 connection.多晶发射极旁的侧墙(spacer-like)结构用来隔开p+ 基极接触和提供自对准.在模拟过程中,relax 语句是用来减小结构深处的网格密度,从而只需模拟器件的一半;第三次硼注入,形成p+基区。

3.遇到的问题

经常遇到这样一种情况:一个网格可用于工艺模拟,但如果用于器件模拟效果却不甚理想。在这种情况下,可以用网格产生工具DEVEDIT用来重建网格,从而以实现整个半导体区域内无钝角三角形3。

本词条内容贡献者为:

石季英 - 副教授 - 天津大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国