微架构又称为微体系结构/微处理器体系结构。是在计算机工程中,将一种给定的 指令集架构在处理器中执行的方法。一种给定指令集可以在不同的微架构中执行。实施中可能因应不同的设计目的和技术提升而有所不同。计算机架构是微架构和指令集设计的结合。

Core微架构的处理器NetBurst微结构的缺陷是IPC(每时钟执行的指令条数)表现不佳,同频情况下Pentium 4有时还不如前代的PentiumⅢ。频率提高后,功耗随之上升,功耗过高,影响了主频的进一步提高。为了改善这种情况,Intel采用了Core微架构。

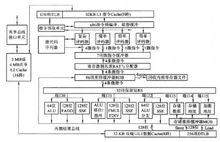

Core微架构是Intel在Yonah微架构基础之上改进而来的下一代微架构,采取共享式二级缓存设计,两个核心共享4MB或2MB的二级缓存,其内核采用高效的l4级有效流水线设计,每个核心都内建32KB 一级指令缓存与32 KB 一级数据缓存,而且两个核心的一级数据缓存之间可以直接传输数据。每个核心内建四组指令解码单元,支持微指令融合与宏指令融合技术,每个时钟周期最多可以解码五条x86指令,并拥有改进的分支预测功能。每个核心内建五个执行单元,执行资源庞大。采用新的内存相关性预测技术。加入对EM-64T与SSE4指令集的支持,支持增强的电源管理功能,支持硬件虚拟化技术和硬件防病毒功能,内建数字温度传感器,还可提供功率报告和温度报告等,配合系统实现动态的功耗控制和散热控制。Core微架构处理器的内部结构如图所示:

Core微架构的处理器系列有用于桌面平台的Conroe、移动平台的Merom和服务器平台的Woodcrest;有Core处理器和Core 2处理器之分,从结构上又可分为单核Core Solo、双核Core Duo和Core 2 Duo以及四核的Core 2 Quad。在多核结构中耦合度的松紧决定四核协作效率的高低,而微架构则决定每个核心的运算效率、实际性能、功耗高低等关键的特性。Intel的Kentsfield/Yorkfield两代Core 2 Quad处理器都基于Core微架构。1

使用微架构的原因使用微架构有很多优势,但是同时也具有一定的风险。下图给出了一个简单的成本效益分析

由上图成本效益分析可以看到,在开发大型应用程序时,使用微架构可以获得最大收益。2

Core微架构的优点Core架构的优势体以下几个方面:

(1)拥有超宽的执行单元。在每个周期,Core架构的指令解码器可以同时发射四条指令,而AMD K8架构只能发射三条指令,换句话说,Core架构拥有更加出色的指令并行度。

(2) Core架构具有“微操作融合(Micro-p Fusion)”和“宏操作融合(Macro-p Fusion)”两项技术,可以对执行指令进行优化,通过减少指令的数量获得更高的效率,Intel表示这两项技术最多可带来67%的效率提升,这也是Core架构产品在低功耗状态下依然拥有强劲效能的主要秘密。

(3) Core微架构的SSE执行单元首度提供完整的128位支持。每个单元都可以在一个时钟周期内执行一个128位SSE指令,而在多个执行单元的共同作用下,Core架构核心可以在一个时钟周期内同时执行1 28位乘法、128位加法、128位数据载入以及128位数据回存,或者是可以同时执行四个32位单精度浮点乘法和四个32位单精度浮点加法,进而显著提升多媒体性能。

(4) Core微架构采用共享Cache设计。Cache资源利用率高于独占式设计,且多个核心可以高效协作。1

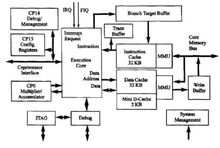

XScale微架构处理器XScale架构处理器是新一代为无线手持式应用产品开发的嵌入式处理器,是PCA开发式子台架构中的应用于系统与通信子系统中的嵌入式处理器。下图是XScale系统结构图:

(1)采用7/8级超级流水线:动态跳转预测;分支目标缓冲器BTB(BranchTargetBarfer)。

(2)支持多媒体处理技术:·新增乘/加器MAC;40位累加器;兼容ARMV5TE指令;特定DSP型协处理器CPO。

(3)指令快存(1-Cache):32KB。

(4)数据快存(D-Cache):32KB:可以重构为28KB片内RAM。

(5)微小数据快存(Mini-DCache):2KB。

(6)指令存储器管理单元IMMU:32路变换后备缓冲器TLB(快表)。

(7)数据存储器管理单元DMMU:32路变换后备缓冲器TLB(快表)。

(8)中断控制器。

(9)总线控制器。

(10)调试(Debug)接口:性能监控:协处理器CPl4;硬件断点;硬件观察点;BKPT指令;异常中断;JTAG接口;迹缓冲器。

(11)动态电源管理。XScale微架构处理器的时钟可以达1GHz、功耗1.6 W,并能达到1200MIPS。3

本词条内容贡献者为:

王宁 - 副教授 - 西南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国