达灵顿晶体管(英语:Darlington transistor),或称达灵顿对(Darlington pair)是电子学中由两个(甚至多个)双极性晶体管(或者其他类似的集成电路或分立元件)组成的复合结构,通过这样的结构,经第一个双极性晶体管放大的电流可以进一步被放大。[1]这样的结构可以提供一个比其中任意一个双极性晶体管高得多的电流增益。在使用集成电流芯片的情况里,达灵顿晶体管可以使得芯片比使用两个分立晶体管元件占用更少的空间,因为两个晶体管可以共用一个集极。达灵顿晶体管通常被封装在单一的芯片里,从外面看就像一个双极性晶体管。有时,集成电路芯片中会包含8个这样的结构方便使用。

起源达灵顿结构是由贝尔实验室的工程师悉尼·达灵顿(Sidney Darlington)在1953年发明的1。他后来将这种两三个晶体接在一起、共同接在一个集电极的创意申报了专利。

另一种看起来与之相似的结构是将两个半导体类型晶体管连接起来(例如NPN-PNP),这种结构被称作是西克对管(Sziklai pair)。

特性一个达灵顿晶体管看起来就像是具有很高电流增益(大约是所使用的两个双极性晶体管的电流增益的乘积)的双极性晶体管。事实上,整个集成电路具有三个引脚(B-基极,C-集电极,E-发射极),这些概念都可以通过标准晶体管的类似概念进行理解。

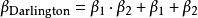

复合结构的电流增益 和两个单一晶体管的电流增益

和两个单一晶体管的电流增益 之间的关系可以表示为:

之间的关系可以表示为:

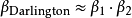

如果β1和β2足够高(达到上百),那么以上关系可以简化为:

现在,达灵顿晶体管产品的典型电流增益可以达到1000甚至更高,因此只需要很小的基极电流就可以让晶体管导通。然而,这样高的电流增益也带来了一些缺点。

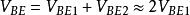

缺点达灵顿晶体管的一个缺点是它的基极-发射极电压被加倍了。由于整个达灵顿结构的基极和发射极之间有两个结,因此等效的基极-发射极电压是各个晶体管的基极-发射极电压之和:

对于硅半导体晶体管,当其处于工作区或饱和状态,其基极-发射极电压VBEi大约为0.65伏特,因此它们组成的达灵顿晶体管结构总的基极-发射极电压大约就是1.3伏特。

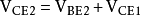

达灵顿晶体管的另外一个缺点是其饱和电压更大。输出级晶体管不能饱和(也就是说其基极-集电极的结必须维持反向偏置),因为当第一级晶体管处于饱和状态时,它将在输出级晶体管的集电极和基极之间施加满幅负反馈。由于输出级晶体管的集电极-发射极电压等于其自身基极-发射极电压和前一级晶体管的集电极-发射极电压之和,两个电压在正常工作状态时都具有正数值,因此它总是超过了基极-发射极电压,即总有

因此

因此

所以,达灵顿晶体管的饱和电压是一个基极-发射极电压(硅管的情况大约是0.65伏特),比晶体管本身的饱和电压(约0.1到0.2伏特之间)要大得多。假设都具有相等的集电极电流,这个缺点会表现为达灵顿晶体管的耗散功率比单一晶体管要大。此外,更高的集电极-发射极电压在晶体管-晶体管逻辑电路(Transistor-transistor logic, TTL)电路中可能会引起逻辑错误。

达灵顿结构导致的另一个问题是,其开关速度不得不降低,因为第一级晶体管不能够主动抑制第二级晶体管的基极电流,因此开关响应比单一的晶体管更慢。为了缓解这一缺点,第二级晶体管的基极和发射极之间常常会连接一个几百欧姆的电阻。这个电阻在基极和发射极之间为积累在基极-发射极结上的电荷提供了一条阻抗较低的释放路径,由此使得达灵顿晶体管的开关速度更快。

在高频率的情况里,达灵顿对将具有比单一晶体管更大的相位移动,因此它在负反馈的情况下会变得不稳定。

达灵顿晶体管常把两个分立的晶体管做成集成芯片的形式。在上图中,左边的晶体管Q1可以是低功率类型的,右边的Q2则需要高功率类型的。整个达灵顿结构的最大集电极电流IC(max)大约等于Q2的集电极电流。2N6282是一种典型的达灵顿结构集成芯片,内部包含了一个上文提到过的关断电阻,在IC等于10安培时具有2400的电流增益。

实际上,达灵顿结构可以对安全电压以下皮肤产生的接触电流进行足够敏感的响应,因此它常被用来构成触控开关的信号输入级。

本词条内容贡献者为:

李晓林 - 教授 - 西南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国