PN结隔离(isolation with p-n junction)是指把需要相互绝缘的各部分,用加有反向偏压的PN结来实现隔离。当对一个PN结施加反向偏压时,它有很高的反向电阻。即一个反向偏压下工作的PN结,可以近似地看作是绝缘体。PN结隔离是一种常用的隔离方法。此法工艺简单,可以在外延过程中直接完成,导热性好。1

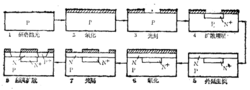

简介PN结隔离是利用反向的PN结在没有击穿的情况下漏电很小,阻抗很大,可以看作绝缘体达到隔离的目的。外延结构的PN结隔离制作过程如下图所示。

将制作电路用的P型单晶硅切成厚约400微米左右的硅片,经研磨抛光后进行隐埋层氧化, 在硅片表面生成厚约1微米的氧化膜,然后经光刻在氧化膜上刻蚀出隐埋层扩散的窗口,接着利用三氧化二锑进行隐埋层扩散,经过扩散后,在刻蚀的氧化膜窗口形成高杂质浓度的N+。

再在扩散过隐埋层的硅片上外延生长适当厚度和电阻率的N型外延层外延层的厚度和电阻串由集成电路的设计指标而定,集电极—基极击穿电压要求愈高, 则厚度愈厚, 电阻率也愈高。接下来进行隔离工艺。先在外延层上生长一层1微米左右厚的氧化膜,同样用光刻方法刻蚀需要隔离的窗口。然后进行浓硼扩散,适当地选择扩散温度和时间,使扩散进去的杂质穿透外延层,形成强P型(P+)的隔离槽与P型衬底相连把整个N型外延片分割成一个个被P型区域包围的隔离岛,由P+型隔离槽与N型外延区之间的PN结, 以防止电路中各个元件通过N型硅外层之间的连通。

特点pn结隔离工艺的优点是方法简单,易于制造,无需特殊技术和制造设备,成本低而同时又能基本上满足电路的性能要求, 因此,成为当前集成电路生产中用得最多的一种隔离方法。然而pn结隔离也存在许多不足之处:

(1)隔离性能不够理想,一般漏电流为毫微安数量级,耐压在几十伏左右,很难做得更高,这是由pn结本身决定的。

(2)隔离引起寄生效应。由于pn结具有电容效应, 因此,pn结隔离后使得晶体管的集电极与衬底之间, 以及集电区周围与p型隔离墙之间有电容耦合,随着频率的升高,其耦合作用增强。因此,在高频放大器和高速数字电路中,这种隔离方法就不适应了。

(3)考虑到隔离扩散时的横向扩散,耗尽层以及套准误差等,隔离墙和元件之间要有一定的距离,在一个晶体管的隔离岛中,晶体管本身的面积只占整个岛的30~40%,对提高集成度十分不利。 ·

(4)pn结隔离的抗辐射能力差,受温度影响大。2

衬底材料的选择为了实现pn结隔离,即n型区被P型区包围,衬底材料必须选用P型硅单晶,以便和n型外延层之间形成pn结。这一pn结击穿电压的大小主要取决于衬底电阻率的高低。从提高击穿电压及减小隔离结寄生电容考虑,衬底的电阻率高一些好。但选得过高,在长时间的隔离扩散中,会增加外延层向衬底的推移,使隔离时间加长。同时,制造高阻P型硅单晶也很困难,因此电阻率不能取得太高。

衬底还起着支撑的作用,所以对其厚度有一定的要求。硅片太薄,在制造过程中容易破碎;硅片太厚,既浪费材料,划片也有困难。一般在抛光后,取厚度为300~350微米较适宜。外延层是在衬底上生长的,它的质量好坏与衬底质量有关,因此要求衬底的位错密度较低,有害杂质(如铁、铜、镍等)少。

PN结隔离改进对通隔离是在标准pn结隔离(又称单面pn结隔离)的基础上产生的。把原来由上而下穿通整个外延层的p+隔离扩散,分为隐埋在外延层下面的p+型杂质层的向上推移扩散(简称下隔离),和p+型杂质的向下扩散(简称上隔离),使它们连通起来, 以达到元件之间隔离的效果,如下图所示。

对通隔离最大的优点是缩短了隔离扩散的时间,并减少了隔离的横向扩散,在一定程度上缩小了管芯面积,提高了集成度,随之寄生电容也减小了。当前对通隔离已用于中、大规模集成电路中。3

本词条内容贡献者为:

张静 - 副教授 - 西南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国