DMI是指Direct Media InterfaceI(直接媒体接口)。 DMI是Intel(英特尔)公司开发用于连接主板南北桥的总线,取代了以前的Hub-Link总线。DMI采用点对点的连接方式,时钟频率为100MHz,由于它是基于PCI-Express总线,因此具有PCI-E总线的优势。

发展历程DMI的首次应用是作为2004年推出的英特尔900系列北桥芯片与ICH6南桥芯片之间的连接接口。此前英特尔推出的芯片组采用一种名为集线器接口(Hub Interface)的接口来连接南桥和北桥,而服务器用途的芯片组使用与之类似但带宽更高一些的企业南桥接口(Enterprise Southbridge Interface,缩写ESI)。DMI尽管命名可追朔自ICH6,但英特尔为了列出芯片的设备兼容性详细数据,而专门使用了“Direct Media Interface”的命名,因此DMI并不能保证允许特定的南桥-北桥芯片的搭配。

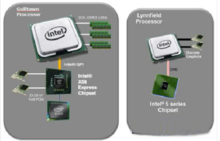

随着Intel Nehalem微架构处理器的发布,老迈的FSB(前端总线)被QPI(快速通道互连)总线(如Bloomfield/Gulftown,Core i7-900系列)、DMI总线(如Lynnfield/Clarkdale,Core i7-800系列、Core i5-700/600系列、Core i3-500系列)取代,为新一代的处理器提供更快、更高效的数据带宽,FSB的系统瓶颈问题也随之得以解决。

技术概况DMI与PCIe总线共用了大量的技术特性,像是多通道、差分信号、点对点连接、全双工、8b/10b编码等。大部分DMI的通信布局类似于PCIe x4规格,不过,最初一些移动计算机平台上则是使用接近PCIe x2的规格,带宽减半,例如915GMS、945GMS/GSE/GU以及Atom N450。DMI使用x4链路时在一个传输方向上能提供10Gbit/s(1.16GB/s)的带宽。

DMI 2.0于2011年发表,使用x4链路布局是能提供2GB/s的带宽,接近两倍于DMI。此时英特尔用它来连接CPU与PCH。

2015年3月9日,英特尔宣布完成了PCH和CPU的融合,使x86 PCSoC配置成为现实,这种设计首次使用在基于Broadwell微架构的Xeon D上。在原本认为DMI会因x86 SoC化而成为历史时,DMI 3.0于2015年8月发布规格,每通道可拥有最大8GT/s的吞吐量,x4规格时有3.93GB/s的带宽。也用于CPU与PCH的连接。部分Skylake的处理器连带PCH集成进CPU芯片上,连接也采用DMI 3.0,不过此时是片上连接,即OPI(On Package DMI interconnect Interface,封装的DMI互联接口),是一个片上系统的布局。

相关技术实现支持DMI的北桥芯片有英特尔的915系列、925系列、945系列、955系列、965系列、975系列、G31/33/P35/X38系列、G41/43/P45/X48系列以及英特尔最后的独立北桥芯片X58。

而支持DMI的处理器,是从集成到处理器上的北桥部分引出,这些处理器有Atom、第一代Core i3/i5/i7(除了Core i79xx系列)。到DMI 2.0时,英特尔已经没有新的独立北桥芯片了,由CPUUncore部分提供DMI界面,使用Sandy Bridge微架构的第二代Core i3/i5/i7、奔腾和赛扬系列及以后的新型号全数支持DMI 2.0,直到使用Skylake微架构的第6代Core系列为止。

支持DMI的南桥芯片有ICH6、ICH7、ICH8、ICH9、ICH10、NM10,支持DMI的PCH:P55/H55、H57/Q57、PM55/HM55、HM57/QM57/QS57。

支持DMI 2.0的PCH设备有Z68、P67/H67/Q67、Q65/B65、H61、HM65、HM67/QM67/QS67、Z77/H77/Q77、Z75/Q75/B75/X79、HM75/HM76/HM77/UM77/QM77/QS77、H81、B85/Q85、Q87/H87/Z87、H97/Z97、C222/C224/C226/X99以及H110。1

支持DMI 3.0的PCH有Z170/H170/HM170/Q170、QM170、Q150/B150、C236、CM236以及C232。2后续发表的英特尔200系列芯片组也支持DMI 3.0。

具体介绍在4系列芯片组没有取消前端总线FSB时,DMI 是Intel(英特尔)公司开发用于北桥(G)MCH(Graphics & Memory controller hub)和南桥ICH10/ICH7之间的芯片连接总线。DMI实现了上行与下行双向数据传输率,单通道单向传输速率达到2.5GT/s,采用8bit/10bit编码,共计4条通道。这个高速接口集成了高级优先服务,允许并发通讯和真正的同步传输能力。它的基本功能对于软件是完全透明的,因此早期的软件也可以正常操作。

从5系列芯片组开始的新构架设计中,前端总线被取消,北桥芯片的功能被整合进CPU中。显卡采用了PCI-E ×16的通道直连CPU,当多卡交火时分为×8+×8(双卡)或×8+×4+×4(三卡)(具体分配方式要参考主板设计)。因为PCI-E2.0的应用,DMI升级到DMI2.0,单通道单向传输速率达到5GT/s。同时DMI2.0也不再用于南北桥芯片的连接,而是用于CPU和芯片组(原南桥芯片组)的连接。

从100系芯片组开始,DMI升级到DMI3.0,单通道传输速率达到8GT/s,采用128bit/130bit编码,有效码率高达98.46%,比8/10编码的80%提高了很多。

DMI总线带宽的计算:

理论最大带宽(GB/s)=(传输速率*编码率*通道数)/8(bit/byte转换)

DMI理论最大带宽=(2.5GT/s*8/10*4)/8=1GB/s

DMI2.0理论最大带宽=(5GT/s*8/10*4)/8=2GB/s

DMI3.0理论最大带宽=(8GT/s*128/130*4)/8=3.94GB/s

随着Intel Nehalem微架构处理器的发布,老迈的FSB(前端总线)被QPI(快速通道互连)总线(如Bloomfield/Gulftown,Core i7-900系列)、DMI总线(如Lynnfield/Clarkdale,Core i7-800系列、Core i5-700/600系列、Core i3-500系列)取代,为新一代的处理器提供更快、更高效的数据带宽,FSB的系统瓶颈问题也随之得以解决。

例如在P55主板上,已经完全看不到北桥芯片的踪影,只剩下了一个名为PCH(平台控制器中枢)的芯片用来支持外设。原来,在P55平台中,北桥功能已经完全被整合在了CPU当中,就连最后的PCI-E总线也被整合到其中。这样一来,CPU对PCI-E总线和内存的控制权就完全交给了自己,这也是LGA1156与LGA1366最大的不同,当然其内部通信依然是数据量惊人的QPI总线。而PCH芯片部分虽然相比原来的南桥芯片功能上更为丰富,但其性质大体相同,它与CPU间同样不需要交换太多数据,因此连接总线采用DMI已足够了。所以,看似只有2.5GT/s的DMI总线实质上是彻底释放了北桥压力,换来的是更高的性能。 虽然Lynnfield(Core i7-800系列/Core i5-700系列)平台在物理上由“CPU-北桥-南桥”的三芯片连接变为“CPU-PCH”的双芯片连接,但是QPI总线连接还是存在的,它连接着Lynnfield处理器的“Core(内核)”和“UnCore(外围核心,如L1/L2/L3 Cache、MCH、PCI-E控制器等)”两部分,而通过DMI总线和PCH芯片通信的是处理器的UnCore部分而不是Core部分,这实际上还是之间那种“CPU到北桥芯片用QPI或FSB总线,北桥芯片到南桥芯片用DMI总线”的连接方式,三芯片与双芯片的连接方式本质上并没有改变。 当然也不能把PCH芯片和ICH南桥芯片相等同,因为除了继承传统南桥芯片的输入输出功能外,PCH芯片还承担了传统北桥芯片诸如Dispaly单元、Management Engine单元、NVRAM单元以及Clock Buffers单元等任务。不过虽然PCH芯片的功能要比传统ICH南桥芯片的功能要复杂一些,但是其和处理器的UnCore部分之间是不需要进行太多通信的,因此一条“古老”的DMI总线足以满足其数据交换需求。

DMI是否取代QPI

答案是否定的。 在发现了 DMI的优势之后还不能忽略的是, 在 CPU内部集成了如此多的控制器,在数据传输方面的要求更高,所以 intel 在 CPU内部依然保留了 QPI 总线,用于 CPU内部的数据传输。这样,这两个总线的传输任务就分工明确了, QPI 主管内, DMI主管外 ,全新的 Lynnfield 核心的 Core i7/i5 处理器离不开高效快速的总线连接,内外如一。

在这里还需要注意一点的是,在 Bloomfield 核心的 i7 系列上, QPI 总线的高速度是为双 PCI-E X16 准备的,需要保证的是整个平台的性能优势,当 PCI-E 控制器移到 CPU内部后,那么这个高速的传输总线当然就可以免去了, 而且从 CPU内部直连 L2 缓存的效果更佳, 低速的 DMI总线也完全可以胜任 CPU与外部芯片的连接。

总之,从技术的发展上来讲, DMI 占据主导地位说明了技术的进步,但是 QPI 仍然是 intel追求技术创新的衍生物,不可被忽视。

本词条内容贡献者为:

王慧维 - 副研究员 - 西南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国