简介定义

随着大规模集成电路的迅速发展,计算机性能已有很大的提高。在其发展过程中,面对技术工艺对单处理机速度的限制,许多计算机科学家提出多种技术(如:流水线技术、并行处理等),目的是为了进一步提高计算机系统性能,这些技术无疑吸取了其潜在的并行性,而多总线多处理机系统(multiplebusmultiprocessorsystem,MBMP系统)正充分利用这一特点而受到人们越来越多的重视。这种系统既解决了单总线系统严重的瓶颈问题,又克服了交叉开关系统通信能力过剩的弊病,是一类很有吸引力的体系结构模型。1

多总线多处理机系统实际上是单总线系统和纵横开关网系统的折衷方案的产物。总线数目可根据实际需要而增减,使系统在性能一定的条件下具有较低的硬件成本。2

多处理机按照传统的定义,有如下特点的计算机系统称为多处理机:

1)包含两个或多个同构或异构CPU;

2)每个CPU都有其自己的I/O通道、控制器和外围设备;

3)每个CPU都有自己的存储器,或者可以与其它CPU共享存储器;

4)整个系统由统一的操作系统控制,在CPU和程序之间实现任务程序、指令级并行处理。

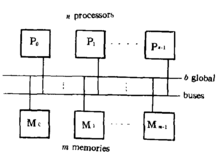

多总线多处理机系统就是把多个处理机和存贮器模块通过若干总线连接起来(如图所示)。

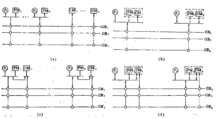

四种典型结构MBMP系统共有四种典型结构,其原理分别如图中(a),(b),(c),(d)所示。 以下依次简称为A1,A2,A3,A4。这四种结构的共同特点是:每个处理机(Pi)都有一个自用存贮器(PMi),用于存贮该处理机要执行的程序及其中间结果。处理机之间的信息交换通过公用存贮器实现。其中,每个公用存贮器模块(CMi)都可由任一全局总线与任一处理机相连,以便几个处理机同时与公用存贮器交换数据。

以下依次简称为A1,A2,A3,A4。这四种结构的共同特点是:每个处理机(Pi)都有一个自用存贮器(PMi),用于存贮该处理机要执行的程序及其中间结果。处理机之间的信息交换通过公用存贮器实现。其中,每个公用存贮器模块(CMi)都可由任一全局总线与任一处理机相连,以便几个处理机同时与公用存贮器交换数据。

A1中的公用存贮器与处理机是分离的,没有从属关系。某一处理机得到其他处理机需要的数据时,就将其通过全局总线写人公用存贮器。处理机从公用存贮器读取数据,也要通过全局总线。

与A1不同,A2、A3、A4的公用存贮器分布于各处理机模块。分布在处理机Pi的公用存贮器模块CMi称作Pi的局部存贮器,当处理机Pi得到Pi需要的数据时,就经全局总线将其写人Pi的局部存贮器CMi中,Pi从CMi中读取这个数据只需经过局部总线。因此,在其他条件相同时,A2、A3、A4占用全局总线的机会少于A1。

A2中公用存贮器模块CMi和处理机Pi的自用存贮器PMi实际上是一个物理实体,只是将存贮空间逻辑上分成两部分而已。所以,CMi的存取操作和PMi不能同时进行。当某处理机访问CMi时,Pi的工作就要被中断`

A3中的公用存贮器CMi和PMi是两个物理实体,可以同时接待来访者。只有当处理机Pi的局部存贮器操作与其他处理机向CMi的写数冲突时,Pi的工作才被中断。

A4中的公用存贮器CMi和PMi虽然也是一个物理实体,但所采用的存贮器是双口的,一个口作为Pi和PMi的通道口,另一个用于CMi所以,A4中的CMi和PMi可认为是互不相关的两个存贮器,能同时接待处理机的访问。3

A1的性能评估问题较其他三种结构简单,分析、研究的文献也最多。其中,比较重要的早期研究者是Bhadnarkalrt。Bhadnarakr在处理机访问公存请求的时间间隔服从几何分布的假设下,将A1的状态及其转换关系用离散马尔可夫链表示.对不多于16个处理机和16个公用存贮器的A1系统给出了性能估计值,Bhandarker的基本假设是:

(1)处理机相同;(2)公存操作时间为常数;(3)访问公存请求概率MRP≤1,即一旦处理机的公存操作结束,立即就有新的访问公存请求;(4)通信网是纵横开关网;(5)处理机以等概率访问所有公用存贮器。

Bhadnarke的假设(3)与实际情况相差甚远,假设(4)限制了其分析方法只适于纵横开关网系统。Towsley将假设(4)放宽为多总线系统,得到了近似解和仿真解。

另一类比较接近实际情况的分析方法基于以下几点假设:

(1)处理机相同;(2)公存操作时间服从指数分布;(3)访问公存请求之间的时间间隔服从指数分布;(4)任意总线数;(5)处理机以等概率访问所有公用存贮器.

其中,Bhandarker等Marsan等给出了近似解;Irani等和Marsan等给出准确解.这些文献中,lrani等的研究比较出色,他们的结果适于任意规模的情况.对于公存操作时间为常数况,Towsley和Holhday等分别给出了近似解和准确解,但只适于小规模的A1系统。3

A2、A3、A4系统分析起来远比A1系统复杂,研究、分析的文献也较少。Marsan等,只分析了单总线的情形。

系统冲突及解决对于一个:n×m×b多总线多处理机系统,冲突常常发生,冲突的类型有以下三种:①当几个处理机同时访间一个处于空状态的存贮模块时,冲突发生;②当一个处理机企图访间一个处于忙态的存贮模块时,发生冲突;③当一个或一个以上处理机想访问某个存贮模块,而此时没有空闲的总线。

为了解决这三种冲突,首先引进优先级机制,即规定n个处理机(P0~Pn-1)的优先级为0~n-1,优先级为0者具有最高优先权,优先级为1者次之。依此类推。

其次,引进两级裁决机制来解决访存冲突。所谓两级裁决机制指第一级裁决即存贮模块裁决和第二级裁决即总线裁决。在第一级裁决中,通过m个:u—users、l—server型裁决器解决存贮模块冲突,每个裁决器选择优先级高的处理机访问存贮模块;在第二级裁决中,通过一个m—users、b—servers型裁决器解决总线冲突问题,这个裁决器主要把总线分配给各存贮请求。1

系统总线设计总线寻址方式因为是一种多处理机系统,需要处理各种相关数据的方式。利用7 条专用的处理机总线来进行系统的通信,可以在一定程度上降低和避免由于地址线来确定地址的处理方式。使用一定的广播式寻址和逻辑式寻址。在系统运行的过程中,7 条专用处理机能够交换和处理各种运行状态、接口标志以及条件等。处理机标号可以从一到七进行编号,在设备停机的时候,可以适当地对标准逻辑进行访问,把主控机数据适当发送到总线上,利用相同的地址线进行数据的处理。4

主控机发送访问地址主机的接口会在开始某个总线周期的时候适当的把地址发送到24 位总线地址上。在周期完成以后,接受方会适当地把地址锁入到总线地址的寄存器中。总线地址单元为X,寄存器会在一定程度上把地址信息锁入到寄存器中,利用译码电路来编译出地址,指定编译出的地址内容,寄存器、程序存储器以及内部存储器等。

主控机读数据在进行数据读取的时候,在总线完成周期以后处理器应该把16 为数信息适当的发送到总线地址上。

主控机保存与恢复在系统中运行的主控机,停止应用程序的时候,如果是利用相同单元来读取数据信息,就会导致出现数据丢失的问题。为了尽可能的避免出现问题,需要适当保持原来的主控机数据信息。主控机中存在的历史存储器需要适当的保留和恢复七个存储器中的所有总线数据内容。利用寄存器F 来对主控机接口进行数据的处理,实际上寄存器F 就是宏单元中的R寄存器。4

主机读处理机状态利用一定的软件适当地读取主控机处理信息数据的状态。每经过25ns就会把相关数据发送到总线中,显示目前的状态,每一相位送出的实际内容为:相位零,主机孔标志寄存器,相位一,运行状态,相位二,机间命令,相位三,运行处理的条件。4

总线全局条件位总线的条件实际上就是说在指定的数据位置可以适当改变高性能多机处理系统的特定执行数据位。例如,在进行计算处理执行的时候,可以合理地把结码寄存器和计算结果进行一定的比较,得到相应用地变量条件,在对最后相位进行执行的时候,把计算结果适当地放置在R 寄存器上。但是如果具有很好的寄存条件的时候,条件位可以在一定程度上改变指令流程。在停机处理的时候,有效的条件变量由条件寄存器来合理表示,仅仅具有一定的读取作用,是一种只读寄存器。条件可以适当地提供相应的可读寄存器,并且在处理的过程中给予一定的数值指令。在运行的时候,可以连续地对比条件寄存器和条件赋能寄存器,如果都是处于置卜状态,放置在主条件位。4

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国