研究背景

电压的测量在电力工业中起着极为重要的作用,它为电力系统提供用于计量、控制和继电保护所必需的信息。目前,世界各国的电压测量仍然主要依靠传统的电磁式电压互感器 PT(Potential Transformer),这种传感器要求在高、低压端之间提供复杂昂贵的电气绝缘,并且随着输配电网朝着高电压、大容量方向发展,高电压等级的 PT 变得越来越笨重,价格越来越昂贵,给运输和安装带来很大困难,同时 PT 本身存在的磁饱和、铁磁谐振、动态范围小、频带窄、易燃易爆、易受干扰,PT 的次级短路危及周围设备及操作人员的生命安全等一系列难以克服问题,这就促使人们研制高性能的互感器及其系统。光纤传感器具有抗电磁干扰能力强、灵敏度高、电绝缘性好、安全可靠、耐腐蚀等诸多优点,在国外已有光学电压互感器挂网运行 [3,4] ,国内也有此类研究工作 ,但理论和实践证明,它们也存在许多问题,如光纤固有双折射、集成光波导的不对称性等,都严重影响互感器的精确度和可靠性。1

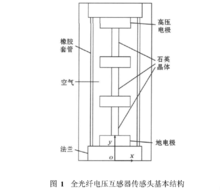

基本原理及传感头结构 全光纤电压互感器采用全光纤方案 , 以石英晶体的逆压电效应和椭圆芯保偏光纤中 LP01 模和 LPe11 模之间的模间干涉原理来实现高电压的测量。如图 1 所示 , 传感头初步结构由 4 块铝质电极和 3 块圆柱型石英晶体组成 , 椭圆芯保偏光纤等张力缠绕在石英晶体上 ( 图中未画出)。

全光纤电压互感器采用全光纤方案 , 以石英晶体的逆压电效应和椭圆芯保偏光纤中 LP01 模和 LPe11 模之间的模间干涉原理来实现高电压的测量。如图 1 所示 , 传感头初步结构由 4 块铝质电极和 3 块圆柱型石英晶体组成 , 椭圆芯保偏光纤等张力缠绕在石英晶体上 ( 图中未画出)。

当互感器工作时 , 石英晶体的两端产生电势差 , 根据晶体的逆压电效应 , 晶体的圆周会产生应变 , 从而导致缠绕在上面的光纤也产生相应的应变 , 这种应变在双模光纤中将调制出一个光学相位差 , 只要能测得这个相位差就可以确定被测电压或电场。由于对相位差的测量较困难 , 因此可以通过干涉法 , 将相位差转化为光强的变化来进行间接测量。传感头的基本结构如图1所示。

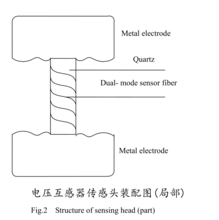

传感头的设计 传感头是互感器的关键部件,其性能直接关系到测量系统的质量。为消除传感光纤中的固有双折射,必须采用适当的组装和退火措施。图 2 给出了电压互感器传感头装配图 ( 局部 ) 。系统中共有三支石英晶体 ,其间用金属电极分开。为便于讨论,本图仅绘出一支晶体。每支石英晶体的直径为 30mm ,长度为 120mm ,金属导体的膨胀系数与晶体的膨胀系数接近。系统中每支晶体各承受三分之一的电压,同时在空气绝缘条件下,能承受 480kV 雷电冲击电压而不损坏,每个石英晶体上均匀地、等间距地缠绕大约 10m 、 24 匝双模传感光纤,缠绕之前,在光纤上涂敷一层 3~5µm 厚的聚酰亚胺薄膜,以保证压电晶体产生的应变全部传到双模光纤中,并且隔离温度的影响以保持光纤的长期稳定性。传光单模光纤约为 20m 长。

传感头是互感器的关键部件,其性能直接关系到测量系统的质量。为消除传感光纤中的固有双折射,必须采用适当的组装和退火措施。图 2 给出了电压互感器传感头装配图 ( 局部 ) 。系统中共有三支石英晶体 ,其间用金属电极分开。为便于讨论,本图仅绘出一支晶体。每支石英晶体的直径为 30mm ,长度为 120mm ,金属导体的膨胀系数与晶体的膨胀系数接近。系统中每支晶体各承受三分之一的电压,同时在空气绝缘条件下,能承受 480kV 雷电冲击电压而不损坏,每个石英晶体上均匀地、等间距地缠绕大约 10m 、 24 匝双模传感光纤,缠绕之前,在光纤上涂敷一层 3~5µm 厚的聚酰亚胺薄膜,以保证压电晶体产生的应变全部传到双模光纤中,并且隔离温度的影响以保持光纤的长期稳定性。传光单模光纤约为 20m 长。

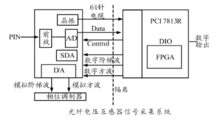

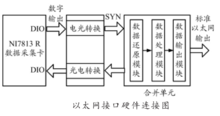

信号采集系统 光纤电压互感器信号采集系统如右图所示, 选用NI7813R 智能数据采集卡,板卡上包含 FPGA 模块,通过 68 针接线端口与信号调理电路板相连,通过 PCI 插槽插入到采集计算机中。

光纤电压互感器信号采集系统如右图所示, 选用NI7813R 智能数据采集卡,板卡上包含 FPGA 模块,通过 68 针接线端口与信号调理电路板相连,通过 PCI 插槽插入到采集计算机中。

对采集系统所得信号检测过程分析如下:

⑴FPGA生成数字方波信号, 转化为模拟方波后加在相位调制器上对光路信号进行调制。

⑵ 光路输出的已调信号经过光电探测器( PIN )转化为电信号送入信号调理电路板,经电路板上的放大、滤波、 A/D 转换、隔离送入数据采集卡。

⑶FPGA 对 A/D 进行采样控制,并把采集的数字信号进行解调处理。

⑷FPGA 把解调的数字输出转化为模拟信号,经相位调制器反馈给光路,实现闭环控制。

⑸ 在采集主机上显示、记录数字输出的值。

这样, 通过 FPGA VI ( FPGA 上实现的程序)和HOST VI (采集主机上实现的程序)的编写,就可实现信号的采集与处理。

FPGA VI软件上使用 LabVIEW FPGA在计算机上设计FPGA VI , 经编译转化为 HDL 语言后, 下载到 FPGA上,完成对 FPGA 的配置。 在 FPGA 上主要包括三个模块的设计:

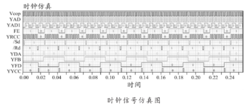

⑴ 各控制时序的生成模块。在基准频率的基础上,通过相应的算法实现 A/D 采样时钟信号、调制方波信号、解调方波信号、 D/A 时钟信号、数字解调时序控制等。

⑴ 各控制时序的生成模块。在基准频率的基础上,通过相应的算法实现 A/D 采样时钟信号、调制方波信号、解调方波信号、 D/A 时钟信号、数字解调时序控制等。

⑵ 信号解调模块。利用相关检测原理,对 A/D 采样输入的信号进行解调。

⑶ 数字阶梯波反馈模块。

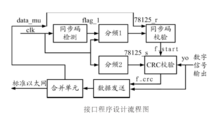

由解调数据运算生成数字阶梯波。时序是整个闭环算法的核心, 因此对时序的生成与时序之间的关系要准确把握,利用 LabVIEW 在主机上进行时序仿真,然后再移植到 FPGA 上实现,这种模式可以大大提高工作效率 , 仿真图如右图所示。

采集卡上的 FPGA 对应有有 160 个 DIO , 分为 4个 connector 接口,每个接口有 40 个 DIO。 使用接口0 connector0 (DIO0-DIO39) 和接口 1 connector2(DIO02-DIO39 2) 定义所需端口。 接口 0 用于连接采集卡和信号调理电路,接口 1 主要分配采样控制信号,调制信号,解调信号以及一些中间过程信号,这些 DIO 端口可以连接到接线端子盒上, 通过示波器查看信号是否正常,从而更加方便的进行调试。

HOST VI使用 LabVIEW 在计算机上设计 HOST 主机 VI ,HOST VI 是对信号的解调结果、数字输出等进行显示、记录、分析的主机功能模块。 因为主机采用的是 DMA的方式对内存进行直接访问, 所以 FPGA 上的解调结果、数字输出等数据能快速地导入到主机程序中,完成数据的实时显示,与此同时,这些数据将被记录到指定的文件中去。 LabVIEW 对数据的读写操作以及波形显示是非常方便和直观的,而且利用 LabVIEW 提供的多种信号处理工具,可以实现数据统计分析、时 / 频域分析、数字滤波、曲线拟合等多种操作。2

以太网接口的硬件实现 实现以太网接口的硬件连接,要用到合并单元,合并单元是电子式互感器与变电站二次设备通讯协议实现的硬件设备, 是连接高压侧数据采集系统和二次设备的桥梁。高压侧数据采集系统将转换完成的电流、电压信息通过光纤传送到低压侧的合并单元, 合并单元按照标准规定的格式发送给二次保护、测控设备。利用合并单元, 在光纤电压互感器信号采集系统上搭建的以太网接口硬件连接图如右图所示。

实现以太网接口的硬件连接,要用到合并单元,合并单元是电子式互感器与变电站二次设备通讯协议实现的硬件设备, 是连接高压侧数据采集系统和二次设备的桥梁。高压侧数据采集系统将转换完成的电流、电压信息通过光纤传送到低压侧的合并单元, 合并单元按照标准规定的格式发送给二次保护、测控设备。利用合并单元, 在光纤电压互感器信号采集系统上搭建的以太网接口硬件连接图如右图所示。

合并单元的 SYN 同 步光信号经光电转换转化为数字 信 号 送 入NI7813R 采 集卡的 DIO 口;采集卡在收到同步信号后,把采集到的光纤互感器的信号处理成合并单元通信协议要求的数据格式,经电光转换送入合并单元,在合并单元中经以下三个模块处理。

⑴基于现场可编程门阵列(FPGA)技术的数据还原模块 在合并单元给多路 A/D 转换器发送同步转换信号之后, 将接收采集通道的输出数据并对其有效性进行校验, 同时将有效数据经过正确排序之后发送给DSP 进行相应的处理。

⑵基于数字信号处理(DSP)技术的数据处理模块数据处理模块利用 DSP 处理器对接收的数据信号进行相关的数字滤波设计,并且对信号进行相位补偿,同时给数据包打上正确的时标。

⑶基于 IEC 61850-9-1 标准的数据输出模块 该模块用于将各路采样值数据进行组帧并发送给保护测控设备。

合并单元的输出即是标准以太网输出。 合并单元与数据采集卡之间数字信号的交换都是通过光纤进行传输的,采用光纤作为传输介质,这使得传输信号的抗干扰能力得到很大提高。

以太网接口的软件实现 数据采集卡通过数字 I/O 与合并单元进行通信, 数据采集卡在收到合并单元发送的同步脉冲信号 SYN 后,将数据发送到合并单元。 按照通信的协议要求, 采集卡数字输出的格式是以 DH 、 DL 、STATUS 、 CRC 的顺序进行发数, 各代码帧结构一样,即再对 SYN 、 D H 、 D L 、 STATUS 、 CRC 五个代码帧进行详细分解,均为: st(1bit)+data(8bits)+dm(1bit)+sp(1bit) 。 其中, st 为起始位, dm为辨别标志位, sp 为停止位, data为数据位,并且在发数的时候数据位应该是低位在前,高位在后。以此为依据,要在采集卡上的 FPGA 上实现各模块程序设计,设计流程图如右图所示,各模块功能如下。

数据采集卡通过数字 I/O 与合并单元进行通信, 数据采集卡在收到合并单元发送的同步脉冲信号 SYN 后,将数据发送到合并单元。 按照通信的协议要求, 采集卡数字输出的格式是以 DH 、 DL 、STATUS 、 CRC 的顺序进行发数, 各代码帧结构一样,即再对 SYN 、 D H 、 D L 、 STATUS 、 CRC 五个代码帧进行详细分解,均为: st(1bit)+data(8bits)+dm(1bit)+sp(1bit) 。 其中, st 为起始位, dm为辨别标志位, sp 为停止位, data为数据位,并且在发数的时候数据位应该是低位在前,高位在后。以此为依据,要在采集卡上的 FPGA 上实现各模块程序设计,设计流程图如右图所示,各模块功能如下。

⑴异步检测 MU信号 每完成一次数据采集,合并单元都会产生一个复位信号, 并发送给采集卡一个SYN 信号, 该模块完成对复位信号和 SYN 信号的检测,从而生成开始采集的标志位。

⑵时钟分频模块 包括数据的接收时钟和发送时钟,在采集卡上设置一个与合并器 25MHz 频率相同的基准频率,以此为基准,延迟 16 个周期后 32 分频,作为同步码接收校验的时钟; 另外直接对基准时钟进行32 分频,作为数据发送的控制时钟。

⑶同步码校验模块 逐位检测合并单元发来的八位信号,比较是否与同步码 8′hA5 相同,生成标志位。

⑷CRC校验模块 采用校验多项式为 x 8 + x 2 + x +1,则对应的二进制数为 100000111 ,由采集的 16 位数据作为高 16 位, 以 8′hA5 作为低 8 位组成一个 32 位的被除数,这和传统的 CRC 校验 [5] 相类似,也相当于把被校验的数据左移了 8 位。用模二除法的法则把这个 32 位的被除数除以 100000111 , 所得余数即为 CRC 校验码。

⑸串行数据发送模块 采集卡在收到同步码信号后,经过同步码检测、同步码校验和 CRC 校验,数字输出便以 D H 、 D L 、 STATUS 、 CRC 的顺序串行发数,采样时间设置为 208.3μs, 则按照合并器 50Hz 的同步码频率,每个周波 20ms , 采样点数为 20ms/208.3μs=96 点 / 周波,每秒的采样点数为 4800 个点。2

应用前景光学电压互感器是近年来发展起来的一种新型的电压测量设备 , 它是利用光电子技术和光纤传感技术来实现电力系统电压的测量 , 因而能够克服传统电磁式电压互感器和电容分压式电压互感器暴露出来的一系列严重缺点 , 如 : 绝缘结构日趋复杂 , 体积越来越大 , 造价越来越高等等 , 因而备受国内外学者和工程技术人员的广泛关注和深入研究 , 具有十分广阔的应用前景。3

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国