图像采集

图像指的是一切图片和影像的总称,是现代信息社会中最常见、最基本的一种数据信息。图像在人们的生活和生产中无处不见,它在人类获取的外部信息中占据着重要的地位。记录图像信息的手段从一开始的胶片技术一直发展到现在应用最广泛的 CCD/CMOS 图像传感器。图像采集系统是一种采集、获取数字化视频图像信息,并依据要求将其上传至计算机、播放或者存储起来的硬件设备。对于现在的普遍应用来说,图像采集基本都是指采集 CCD/CMOS 相机输出的图像信号。采集精度、采集速度和采集系统的存储量是图像采集系统的关键要素。尤其是高速图像采集系统中,数据量普遍偏大,所以对数据的储存和传输有着更加严格的要求。1

应用背景随着现代电子技术的飞速发展,高速图像采集技术在越来越多的领域都有了广泛的应用,例如图像处理、电视会议、治安监控系统、交通监控、工业控制、军事、医学、航天等方面。可以说在我们生活的方方面面都能涉及到图像采集技术,应用领域各不相同也就带来了对技术的不同要求。最常见的图像采集器件就是图像采集卡,而目前市场大部分的图像采集卡都对图像数据传输格式有一定限制,而且采用的是“相机—图像采集卡—计算机”这样的连接传输模式,直接传输到计算机上,这种方式功能单一、传输速度有限,并且需要直连计算机受工作环境限制较大。所以设计一种高速、使用方便的图像采集系统将能符合许多领域的应用需求。

研究现状图像采集系统的发展方向有非常大一部分因素是由 CCD/CMOS 传感器的发展决定的。从 1969 年 CCD 器件发明以来,人们对这类传感器的研究就从来没有间断过。至 20 世纪 90 年代分辨率突破百万像素并开始在数字相机中广泛应用。直到现在由于半导体制造工艺的飞速发展,大 CCD/CMOS 传感器的分辨率已经达到数千万像素,大面阵、小像元的 CCD 传感器层出不穷,美国 EG&G.Retion就研制出 8192×8192 像元的高分辨率 CCD 图像传感器。另外 CMOS 传感器虽然成像质量相较于 CCD 传感器略差,但是读取速度却非常快,加拿大 Dalsa 公司开发的 CMOS 传感器最高读出速度可达 20000 帧/秒。所以几乎所有数字相机的输出图像数据量都有个明显的增长,这就必然要求图像采集系统采集跟上高速大量的相机输出数据,这也是现今高速图像采集系统的发展趋势。 早期的图像采集由于计算机总线速度实在太低,视频图像完全不能实时采集并送入计算机或存储下来,所以通常采用胶片式高速摄影机将运动事件以图像的方式记录下来。等到胶片冲洗完,直接在胶片上进行观察分析。这种方法的缺点很多,使用时占用众多设备,采集到所需图像耗时长,整个过程效率极低。到现在这种方法已渐渐淘汰。 上世纪九十年代前,主要是以模拟信号为主的图像信息采集处理系统。在工业应用、视频监控等系统中,图像信息主要是以模拟信号为主,但是模拟信号的固有局限性难以满足更高的应用要求,数字化是必然的方向。2

高速数据采集系统分类如今,随着数字相机和计算机技术的飞速发展,图像采集技术主要就是采集数字相机的图像数据,一般常见的有如下几种系统:

PCI 图像采集卡第一类是最常见的 PCI 图像采集卡,图像采集卡与主板间采用 PCI 接口连接,图像数据流向是“相机—图像采集卡—计算机”这样的模式。图像采集卡使用非常简单,成本也不高,其作用只是将数据直接上传到计算机,所有的后续存储和处理都是在计算机上实现的。图像采集卡采用 PCI 的理论带宽峰值是 132MB/s,实际应用中一般因为与其他 PCI 设备产生冲突等原因很难能达到峰值带宽。这种图像采集系统还有一大缺点是必须连接电脑,在很多户外环境下使用极不方便。而且其百兆出头的采集速度在先进很多设备上难以满足采集速度要求,所以一些此类图像采集卡上都带有数据压缩功能,尤其是对于视频采集上,不同档次的采集卡具有不同档次的压缩性能。对数据的压缩在不太注重质量的情况下可以不考虑,甚至压缩之后还便于存储,但另外一些有严格要求的情况就难以满足使用需求了。

控制芯片第二类系统是在硬件采集过程中加入控制芯片进行一些相对简单的图像处理,如灰度均衡、彩色图像二值化或图像重构等。早期系统中,多使用单片机或者DSP 控制来实现此功能,但随着数据量越来越大,这种方式已经很难满足要求。现在高速度的 FPGA 以及部分专用数字处理芯片的出现以及流行为这种图像采集和处理系统带来了新的解决方案。目前在图像方面已经有了很多成熟的IP Core,如滤波器、颜色空间转换、图像编码器等[12],利用 FPGA 来实现数字信号处理系统的计算已经比较普遍了。FPGA 具有高速、开发时间短、灵活性高、可并行处理等优点。相比于纯软件的串行工作方式,FPGA 硬件的并行和流水线工作方式在速度上占有很大优势,而且同时可以利用 FPGA 进行外部逻辑控制,在一定程度上也提高了系统的集成度。近年来就有非常多对基于 FPGA 集合图像处理的图像采集系统的研究。

板载存储第三类是实现图像采集并把采集到的图像数据直接进行板载存储,不必须连接计算机的方案。这种方案相较于直接连接计算机,将数据全部传输到计算机上的方法有一个比较明显的优势,就是使用方便。若要直接上传至计算机,那么不论采集条件和环境如何,都必须要携带一台计算机才能进行相关工作,这在户外有些情况下是非常麻烦,甚至不可能达到的。如果是板载存储,那么采集设备体积就很小,可以任意携带,环境适应性大大加强。这种方式在早期,主要是限制于存储器的速度和容量。早些时候小体积的存储器存储空间有限,当要求存放大容量的图像信息时就要对图像进行压缩,这样难免会丢失部分图像信息。一些较好的方法可以在某些程度上带来一些存储上的优化措施,例如存储少量图像时进行高分辨率的原图存储,而需要继续存储更多图像信息时,就把先前存入的高质量图像压缩来空出存储空间以存储后来的图像。这种弹性储存法能在有限的空间内存储尽量高质量的图像,但存储过程中需要大量的运算,必然导致存储速度降低。之前对于这方面的研究还比较少,现在由于半导体工艺的发展,高速度大容量小体积存储器的出现,鉴于板载存储广泛的适用性,对这种系统的研究具有很高的实用意义。2

高速数据采集系统设计利用近年来提出的一些高速度、高性能的接口,采用现在应用很广的 Nand Flash大容量存储芯片提出一种板载存储的高速图像采集系统。

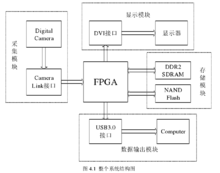

利用高速接口和存储器,设计出一种高速图像采集系统方案。整个高速图像采集系统构成如图所示,包括数据输入采集模块、显示模块、存储模块、数据输出模块和核心控制芯片 FPGA。

FPGA 是系统的控制核心,所有模块都由 FPGA 联系起来,图像数据每一步的流向都是由 FPGA 来控制的。

数据输入采集模块的作用是接收数字相机传输来的图像视频信号并且传到FPGA 上以供后续操作。采集接口只有一种,就是当下非常流行的高速相机接口Camera Link。Camera Link 接口接收相机传输来的 LVDS 信号转化为系统内部使用的 TTL 信号送给 FPGA。

显示模块是一种可选择的辅助作用,用于在采集过程中观察所采集到的图像或者采集后重放存储芯片内储存的图像信息。显示模块的接口是 DVI 接口,使用时连接 DVI 显示器方可工作。

存储模块是此高速图像采集系统的核心,FPGA 接收到采集的图像数据,经过高速缓存,最终储存在系统内。使用DDR2 SDRAM 来进行数据缓存,最终存储在 NAND Flash 存储器内。 所存数据最终是要上传到计算机来进行处理或者存储的,数据输出模块就是这个作用。

与计算机连接使用的是 USB3.0 接口,USB 接口是计算机上最常见的接口,新版本的 USB3.0 也在各方面性能有了很大的提高。

FPGA本 系 统 使 用 的 FPGA 是 Xilinx 公 司 生 产 的 Spartan-6 系 列 芯 片XC6SLX25-3FG484C。Spartan 系列是 Xilinx 公司面向普通工业、商业的领域的低成本系列芯片。新一代 Spartan-6 系列不仅拥有业界领先的系统集成能力,同时还能实现适用于大批量应用的最低总成本。与上一代 Spartan 系列相比,该系列芯片功耗仅为其 50%,且速度更快,连接功能更加丰富全面。

电源模块电源是系统设计中非常重要的一部分,如果电源不稳定,就会对电路的正常工作造成影响,不但电路运行会出现问题,而且会影响器件的使用寿命。在电源设计上,为了保证每个器件都能正确获得其所需电压,就要考虑电源传输过程中的阻抗,也要顾及尽量消除电源噪声等影响。

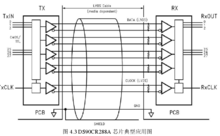

采集模块采集模块就是 Camera Link 接收部分,使用的是 National Semiconductor 公司的 LVDS 接收芯片 DS90CR288A,此芯片接收四对 LVDS 信号并转化为 28 位LVTTL/LVCMOS 数据,最高支持 85MHz 像素时钟,也就是 2.38Gbit/s 的数据传输速度。芯片典型应用如图所示,左半部分是相机内的 TTL/CMOS 信号转化为 LVDS 信号输出,右半部分是本系统接收连接线传来的四对相机 LVDS 信号和一对时钟信号经过 Camera Link 接口后,由 DS90CR288A 芯片转化回 28 路LVTTL/LVCMOS 信号。

显示模块显示模块的视频接口使用的是 DVI 接口,在系统设计中既包含 DVI 视频输入接口,也包含了 DVI 视频输出接口。其中输入接口的目的是在系统调试过程中,利用 DVI 输入的图像数据进行后面存储功能的调试,就不详细介绍了。而 DVI输出接口的作用则是对采集模块 Camera Link 采集来的图像数据进行显示,可以采集来实时显示,也可以用来显示之前存储在系统中的图像信息以作验证之用。

存储模块存储模块是 FPGA 接收到 Camera Link 接口采集来的图像数据先经过 DDR2 SDRAM 缓存,然后存入 NAND Flash 中。所以该模块主要包含 DDR2 SDRAM 和NAND Flash 两个部分。

数据输出模块图像采集系统的作用是把采集到的数据上传到计算机上,本设计虽然着重于使用方便的图像采集板载存储,但最后肯定要把图像上传到计算机进行存储、处理、分析等工作。USB 接口几乎是现在最流行的计算机接口,USB3.0 的提出也解决了之前版本速度偏低的问题,可以将图像数据快速传输到计算机上。

核心问题就所要实现的功能来看,高速图像采集系统所做的就是保证图像数据流可靠地按照预先安排好的路径传输、显示、存储。其各模块之间的速度匹配关系的优劣在很大程度上决定了整个系统的性能好坏,要尽量做到不过度浪费某一模块的数据传输能力,同时也要保证不能造成前面模块传输来的数据量超过后面所能处理、存储的能力导致数据错误或者丢帧现象。这在设计上必须要考虑到每一模块的速度以及模块之间的速度匹配问题,这也是系统能够高效、稳定工作的一个关键。2

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国