基本概念

在过去几年里,关于微处理机的大量报导和数以百计的微处理机的涌现,为设计者们进行有效设计提供了丰富的资料。这些产品的制造家提供了有关产品的详细文献。但不足的是,迄今还缺乏对微处理机全貌及其发展情况、趋向的论述。现有的资料多为以大量的图表方式列出微处理机各种参数,诸如速度、指令数、寻址方式、寄存器组等。

早期的微处理机(TPU)是一种“半智能”单元,其程序靠CPU来编写。微处理器(又称为CPU或中央处理单元)是装配在单颗芯片上的一个完整的计算引擎。第一颗微处理器是1971年问世的Intel 4004。

早期微处理机介绍在TPU发展过程中,关键的一步是可编程序问题。早期的TPU是一种“半智能”单元,其程序靠CPU来编写。比如用英特尔8257 DMA控制器。虽然一般情况下TPU是在CPU控制之下工作的,但其自身的发展逐渐引起了一种演变,使得通用TPU和通用CPU之间的区别被抹掉了。随着引进英特尔8748/8048单片微处理机和8041/8741 TPU,这种区别就几乎消失了。

8748是一个只用一种5V电源的单微处理机,主要由以下几部分构成:

(1)CPU—8位,70条指令,21种条件转移

(2)P/ROM—1 K x 8程序存储器,带有4K直接地址

(3)RAM—64 x 8随机存储器,包括8级程序计数器(PC)堆栈(可用来做数据存储)。8对寄存器单元可做工作区和为向外扩展为256x8的直接寻址页号

(4)时钟—RC或晶体控制

(5)电源离合—提供时序电容的需要

(6)I/O线—27条和TTL相容

(7)控制线—5条,提供给yo和存储器

(8)中断—外部的:到单元3的向量,间隔时间计数器,为溢出而设的到单元7的向量

(9)逻辑“与”及“或”—直接连向I/O接口及在测试线上的条件转移

8048是单5V微处理机,周期2.5微秒,可进行2进制及2~10进制算术运算。8728有一个可使用紫外线擦掉的P/ROM,一块基片上装有1k个单元。用它做8048的只读存储器(ROW)。

第一代微处理机的特点是低速P-MOS技术,在芯片上译码部份极少,结构简单。英特尔8008就是一台典型的第一代8位微处理机。自从出现了第一台英特尔8080,N-MOS以后,它实现了在芯片上的译码和一套相应的指令系统,就清晰地画出了从第一代发展到第二代微处理机的界限。但是,由于以功能来划分类别的多样化使得区分第二代与第三代微处理机就比较困难了。

如果撇开双极(TTL)可编微程序系统不谈,而只考虑单片微处理机时,那么第二代—第三代的划分就集中在多处理器的协调上,诸如National SC/MP和带有P/ROM的英特尔8048,具有存储器一存储器结构的TI 9900,和功能集中的Mostek 3870单片微处理机。

随着大面积封装密度的增加,在CPU里包含专用的TPU子系统的做法更为现实了。在CPU芯片上装有电可改写的ROM将加速取数时间,并去掉了CPU和存储器之间的信息、通道,相形之下,比用连线方式来使用I/O要方便得多。进一步发展模拟一数字和数字一模拟技术将提供一种可以模拟I/O一些明显功能的设备。正如早先讲到的那样,经济因素预示着带有P/ROM的超一联结式的通用基片的发展可以提供一种在部分场所中使用的结构形式。速度的提高使得NWOS技术已超过了TTL而且其发展的极限还未达到。许多新技术的出现为微处理机的基础系统设计提供了广阔的前景1。

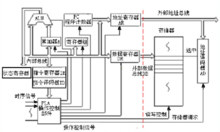

结构微处理器基本结构如图:

这是一个进行了最大程度简化的微处理器。此微处理器具有:

(1)一条地址总线(总线宽度可以8位、16位或32位),用于向内存发送一个地址;

(2)一条数据总线(总线宽度可以是8位、16位或32位),能够将数据发送到内存或从内存取得数据;

(3)一条RD(读)和WR(写)线路,告诉内存它是希望写入某个地址位置还是获得某个地址位置的内容;

(4)一条时钟线路,将时钟脉冲序列发送到处理器;

(5)复位线路,用于将程序计数器重置为零(或者其他内容)并重新开始执行。

微处理器执行一组机器指令,这组指令可向处理器告知应执行哪些操作。微处理器就会根据指令执行三种基本工作:

(1)通过使用ALU(算术/逻辑单元),微处理器可以执行数学计算。例如:加法、减法、乘法和除法。现代的微处理器包含完整的浮点处理器,它可以对很大的浮点数执行非常复杂的浮点运算。

(2)微处理器可以将数据从一个内存位置移动到另一个位置。

(3)微处理器可以做出决定,并根据这些决定跳转到一组新指令。

微处理器能够执行许多非常复杂的工作,但是所有工作都属于这三种基本操作的范畴。

微处理器指令虽然上面的微处理器非常简单,但是它仍然可以执行相当多的指令。指令集通过位模式的方式实现,每一个位模式在加载到指令寄存器中后都有不同的含义。由于人们不能很好记住这些位模式,所以定义了一些简短的单词来表示不同的位模式。这些单词的集合称作处理器的汇编语言。汇编程序可以将这些单词轻松翻译成它们的位模式,然后会将汇编程序的输出放在内存中供处理器执行。

例如以下汇编语言指令:

发展可用晶体管的数量对处理器性能有巨大影响。在8088这样的处理器中,通常要花费15个时钟周期才能执行一条指令。由于乘法器的设计方式,在 8088上进行16位的乘法运算大约需要80个时钟周期。而晶体管越多,就越有可能在一个周期中执行更多的乘法运算。

晶体管数量的增多还使我们能够使用一种称为流水线的技术。在流水线式的体系结构中,指令的执行过程是相互重叠的。所以,虽然需要花费5个时钟周期来执行每条指令,但是可以同时执行5条指令的各个阶段。这样,表面看起来在每个时钟周期内即可执行完一条指令。 许多现代的处理器具有多个指令解码器,每一个都有自己的流水线。这样便存在多个指令流,也就是说每个时钟周期可以完成多条指令。但是这种技术实现起来非常复杂,因此需要使用大量的晶体管。

处理器设计的发展趋势主要是:完全32位的ALU(内置快速浮点处理器)和多指令流的流水线式执行方式。处理器设计的最新进展是64位ALU,预计在下一个十年中家用PC就会用上这种处理器。此外,还存在为处理器添加可高效执行某些操作的特殊指令(例如MMX指令)的趋势,以及在处理器芯片中增加硬件虚拟内存支持和L1缓存的趋势。所有这些趋势都进一步增加了晶体管的数量,导致现在的处理器包含数千万个晶体管。而这些处理器每秒大约可以执行十亿条指令。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国