在数字控制设备中,经常要用到时序脉冲发生器(又称节拍脉冲发生器或脉冲分配器)。它有许多条输出线,在这些输出线上能依次出现节拍控制电位(或时序脉冲),用以协调机器各部分的动作。计数式时序脉冲发生器主要由计数电路和译码电路组成。主脉冲(计数脉冲)送入计数电路,译码电路译出相应的计数状态,即可得到需要的输出1。

采用触发器、移位寄存器、计数器与译码器、脉冲分配器、接口电路与译码器等均能实现时序脉冲发生器,并且具有广泛的实用性及通用性。

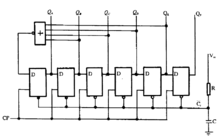

采用触发器组成时序脉冲发生器利用D型触发器可组成时序脉冲发生器,电路如图1所示。将多级D型触发器逐级串接,将它们的 清除端接至由R、C组成的上电复位电路,并将它们的输出端

清除端接至由R、C组成的上电复位电路,并将它们的输出端 ~

~ (最末级输出端

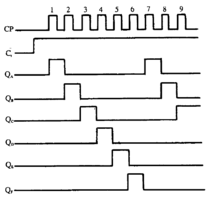

(最末级输出端 除外)经或非门后再反馈至首级触发器的D输入端,便可依次在每个触发器的Q输出端获得时序脉冲,其波形图如图2所示。

除外)经或非门后再反馈至首级触发器的D输入端,便可依次在每个触发器的Q输出端获得时序脉冲,其波形图如图2所示。

这种时序脉冲发生器在开机接通电源后能自行启动,并保持每个时序脉冲的时间为一个时钟脉冲的周期,因而时序脉冲与脉冲之间不会出现“重叠”或错乱现象。电路采用同步触发方式,从理论上讲,所有触发器都应该是同时翻转的。但是,实际上各个触发器的性能不可能完全一样,而且每个触发器的负载大小和布线情况也不相同。因此,这些触发器不可能绝对同时翻转,也就不可能彻底消除竞争冒险现象。图中选用的是74LS174六D触发器和74LS2fi。五输入或非门组成的时序脉冲发生器。依同样道理,可选用74LS74,74LS175,74LS273等其它型

号D型触发器和74LSa2,74LS27,7425等或非门及相应扩展电路组成时序脉冲发生器。

图1

图1

图2

图2

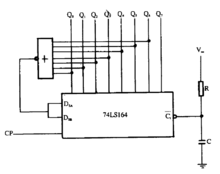

利用移位寄存器组成时序脉冲发生器的电路如图3所示,由八位移位寄存器74LS164附加一个组合七输入端或非门电路组成8时序脉冲发生器。接通电源C,清除端获负脉冲,寄存器清零,输出端 ~

~ 全为“0”,数据输入端

全为“0”,数据输入端 、

、 则为“1”,待时钟脉冲CP正跳沿来到时,

则为“1”,待时钟脉冲CP正跳沿来到时, 输出第一个正时序脉冲并使

输出第一个正时序脉冲并使 、

、 为0,随着时钟脉冲CP的输入,移位寄存器执行右移操作,同步地将这个正脉冲移位,直到

为0,随着时钟脉冲CP的输入,移位寄存器执行右移操作,同步地将这个正脉冲移位,直到 输出正脉冲

输出正脉冲 、

、 又为“1",在时钟脉冲CP作用下

又为“1",在时钟脉冲CP作用下 又输出正脉冲…,如此周而复始不断循环,完成时序脉冲输出。如果时钟脉冲是一个基准时间,则各输出可作为分时定时信号。

又输出正脉冲…,如此周而复始不断循环,完成时序脉冲输出。如果时钟脉冲是一个基准时间,则各输出可作为分时定时信号。

图3

图3

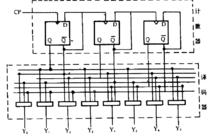

利用计数器与译码器组成的时序脉冲发生器原理电路如图4所示。作为时间基准的时钟脉冲加在计数器输入端,然后经过译码器将计数器的状态译成输出线上的顺序脉冲。图中计数器是异步式的,在时钟脉冲作用,各个触发器不是同时翻转,而是有先有后。在每次状态变化时,可能有两个或两个以上的触发器翻转,因此将出现竞争冒险现象,可能在译码器输出线Y0~Y1上产生干扰脉冲。例如当计数器状态由001变为010时,若触发器A先翻转为0,B后翻转为1,那么在A已翻转,而B尚未翻转时,将出现短暂的000状态,因而会在Y0输出线上产生一个窄的过渡干扰脉冲。同理,Y2输出线在由011变100时,Y4输出线在由101变110时等等,均可能有过渡干扰脉冲产生。要消除过渡干扰脉冲,可采用环形计数器,格雷码计数器或约翰逊计数器,而最简单的办法是用计数输入脉冲去封译码器2。

图4

图4

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国