可重构体系结构目前已成为学术界和工业界的研究热点,并且已经有许多令人瞩目的研究成果和工业产品面世。可重构计算系统提供了一种介于通用计算机和专用计算系统 ASIC之间的计算手段。通用计算机是面向通用应用领域进行设计的,其设计目标主要是能够灵活地处理不同的计算任务,这使得通用计算机具有很大的灵活性和应用范围,但对某些特殊的应用领域却难以取得高性能。专用集成电路 ASIC 是针对某种特殊应用设计的计算系统,对于特定的计算任务,ASIC 表现出极高的性能,但无法处理特定计算任务之外的其它任务。通用计算机和 ASIC 代表了两种极端的计算手段,通用计算机具有最大的灵活性和低性能,ASIC 具有最高的性能和最差的灵活性。而现在有许多应用需求既要求较高的性能,又需要一定的灵活性。例如,一个多媒体应用中可能包括数据并行处理、位处理、不规则计算、高精度字操作、具有实时要求的操作等子任务,要求处理系统能够灵活地处理上述各个子任务并达到一定的性能。许多其它应用也具有类似的需求,如数据加密、人工智能等,这些应用需求导致了可重构体系结构的产生1。

可重构体系结构如果某一计算系统能够利用可重用的硬件资源,根据不同的应用需求,灵活的改变自身的体系结构,以便为每个特定的应用需求提供与之相匹配的体系结构,那么这一计算系统就称为可重构的计算系统,其体系结构称为可重构的体系结构。按照不同的分类标准,可以将可重构体系结构分为不同的类型,下面介绍一些常用的分类标准。

粒度粒度是指系统中可重构成分(或称可重构处理单元,RPU)的操作数的宽度。RPU 是功能可配置的逻辑块,其内部连接关系是可重构的。在一个细粒度的可重构体系结构中,RPU 中的处理元素通常是逻辑门、触发器、查找表等,它们进行位级操作,实现一个有限状态机的布尔函数。而在粗粒度的可重构体系结构中,RPU 中的处理元素可能包括完整的功能单元,象算术逻辑单元 ALU、乘法器等,它们进行字(由多个位构成)级的操作。如果一个可重构体系结构中包括粗粒度和细粒度两种RPU,则称其为混合粒度的可重构体系结构。

编程深度编程深度是指存储在 RPU 中的配置程序或文件的数量。一个 RPU 可能含有单个配置文件或多个配置文件。对于单配置文件系统,只有一个配置文件驻留在 RPU 内,因此 RPU 的功能局限于当前装载的配置文件。而在多配置文件系统中,同时有多个配置文件驻留在 RPU 内,这使得可以通过切换配置文件很方便地实现不同的功能,而不必从外部重新装载配置文件。

可重构能力在处理不同应用的过程中,一个 RPU 可能需要被频繁地重构。重构实际上就是重新装载配置文件的过程。如果装载配置文件的过程必须在中断程序执行的情况下进行,那么这种重构称为静态重构;如果装载配置文件的过程可以和程序执行同时进行,那么这种重构称为动态重构。单配置文件的可重构系统通常具有静态重构的特性,而动态可重构系统往往基于多配置文件的 RPU。动态重构系统中的 RPU,可以在运行部分配置文件的同时,改变其它配置文件。这一特性能够大幅度地降低重新配置的时间开销。

界面如果一个可重构系统的主机和可重构处理单元 RPU 不在同一芯片上,那么称这一可重构系统具有远界面;反之,如果主机和可重构处理单元 RPU 在同一芯片上,则称这一可重构系统具有本地界面。对于具有本地界面的可重构系统来说,RPU实际上已经融合在主机的数据通路中去了。

计算模型许多可重构系统遵循单处理器计算模型,有些可重构系统遵循单指令流多数据流 SIMD 或多指令流多数据流 MIMD 计算模型,另外还有一些可重构系统遵循 VLIW 计算模型。表 列出了当前一些典型的可重构计算系统的主要特征及应用领域。

列出了当前一些典型的可重构计算系统的主要特征及应用领域。

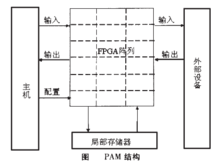

虽然各个可重构计算系统的结构有很大的区别,但其基本组成成分基本上是相同的,即:通用处理器、可重构处理单元RPU、存储器、接口界面。图 是一个典型的可重构计算系统的结构图。其中通用处理器用于控制和处理通用的计算任务,可重构处理单元 RPU 用于处理专用领域的计算任务,在某些系统中处理器与 RPU 集成在同一块芯片上,而在另外一些系统中,处理器与 RPU 分别位于不同的芯片上。两个图

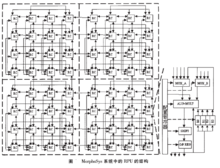

是一个典型的可重构计算系统的结构图。其中通用处理器用于控制和处理通用的计算任务,可重构处理单元 RPU 用于处理专用领域的计算任务,在某些系统中处理器与 RPU 集成在同一块芯片上,而在另外一些系统中,处理器与 RPU 分别位于不同的芯片上。两个图 分别给出了PAM 可重构系统和 MorphoSys 可重构系统的体系结构。PAM系统采用通用计算机外挂 FPGA 阵列的结构;而在 MorphoSys系统中 RISC 微处理器与可重构处理阵列集成在一块芯片内,即处理器与可重构处理阵列是紧密耦合的

分别给出了PAM 可重构系统和 MorphoSys 可重构系统的体系结构。PAM系统采用通用计算机外挂 FPGA 阵列的结构;而在 MorphoSys系统中 RISC 微处理器与可重构处理阵列集成在一块芯片内,即处理器与可重构处理阵列是紧密耦合的 。

。

可重构计算系统的可重构处理单元 RPU (或者称为可重构协处理器)主要有两种类型,一种是现场可编程门阵列 FPGA,另一种是针对特定应用需求设计的可重构处理单元。例如上述 PAM 系统中采用 FPGA 作为可重构处理单元,而 MorphoSys 系统则采用了面向图象处理、数据加密、DSP 变换等领域设计的可重构元素(RC)阵列作为它的可重构处理单元。它们的结构分别如图所示。FPGA 的 基 本 组 成 成 分 是 可 配 置 的 逻 辑 块 CLB(configurable logic block)或 者 称 为 PAB(programmable active bits)。通常每个 CLB 包括组合函数模块、触发器和内部连线,组合函数模块的输入变量数通常在 2 到 6 之间,组合

可重构计算系统的可重构处理单元 RPU (或者称为可重构协处理器)主要有两种类型,一种是现场可编程门阵列 FPGA,另一种是针对特定应用需求设计的可重构处理单元。例如上述 PAM 系统中采用 FPGA 作为可重构处理单元,而 MorphoSys 系统则采用了面向图象处理、数据加密、DSP 变换等领域设计的可重构元素(RC)阵列作为它的可重构处理单元。它们的结构分别如图所示。FPGA 的 基 本 组 成 成 分 是 可 配 置 的 逻 辑 块 CLB(configurable logic block)或 者 称 为 PAB(programmable active bits)。通常每个 CLB 包括组合函数模块、触发器和内部连线,组合函数模块的输入变量数通常在 2 到 6 之间,组合 函数通常用查找表的方式实现,函数的真值表保存在局部寄存器,通过改写真值表的内容,就可以改变函数关系;CLB 的内部连接关系是可重构的。各个 CLB 之间的连接结构通常采用二维网格(mesh)结构。

函数通常用查找表的方式实现,函数的真值表保存在局部寄存器,通过改写真值表的内容,就可以改变函数关系;CLB 的内部连接关系是可重构的。各个 CLB 之间的连接结构通常采用二维网格(mesh)结构。

MorphoSys 系 统 中 的 RPU 是 由 可 重 构 元 素 RC(reconfigurable cell)构成的 8*8 阵列。每个 RC 包括一个配置。寄存器、两个选通器、一个 ALU、一个乘法器、一个移位器、一个由 4 个 16 位寄存器构成的寄存器堆。8*8 阵列分成 4 个子阵列,4: 之间的连接采用二维网格连接和子阵列内的行 / 列完全连接。

可重构系统比较所谓基于 FPGA 的可重构系统是指以 FPGA 为可重构处理单元的系统。FPGA 是细粒度的重构器件,其重构的基本元素是逻辑门、触发器和连线,允许设计者使用门级的器件,因此FPGA 具有很大的灵活性,尤其适用于处理复杂的位计算。但是 FPGA 中的大量的可编程控制电路,在提供了很大的灵活性的同时,也使得寄生电容和数据传输路径的长度增加,有效逻辑门的密度降低,从而增加了信号传输的延时,降低了运算速度。另外,FPGA 处理粗粒度操作的性能较差。基于 FPGA 的可重 构 系 统 的 例 子 有 :Splash、DEC PeRLe-1、Chimaera、DISC、PAM等。

问题当前可重构体系结构的优点及存在的问题当前的可重构体系结构的优点可归纳如下:

能迅速地实现设计的硬件原型,进行逻辑模拟并可以作为ASIC的便宜的替代品。

能够改变位宽(相反,常规的处理器一般具有固定的位宽)以便针对特定的应用提供相应的计算能力,因此具有达到最大并行性的潜力,能够节省功耗。

对于多上下文的操作,能够根据用户的需求构成深度的空间或时间流水线。

硬件虚拟化允许多配置文件和动态部分重构。

具有揭示数据流中的数据并行性的能力。

FPGA和其它成分的混合使用提供了从细粒度到粗粒度的多种不同粒度的操作。

当前的可重构体系结构中还存在下述问题:

浮点性能差。这可以通过集成一个具有良好的浮点性能的处理器核来解决。

有限的资源。这一问题将因百万门的FPGA面世而得到缓解。

数据交换的效率低。制造商将在下一代产品中集成进存储器来解决这一问题。

功耗大。如Xilinx 4003在20MHz的功耗达到2W。

细粒度的体系结构不能适应数据通路型的粗粒度的多媒体计算。将粗粒度和细粒度结合在一起的FPSC现场可编程片上系统(Field Programmable System on Chip)有可能适应上述情况。

90%的芯片面积被连线占用,这严重地降低了效率。

很长的配置时间和编译时间。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国