应力记忆技术( Stress Memorization Technique,SMT),是90nm逻辑技术节点以下兴起的一种着眼于提升NMOS器件速度的应力工程。SMT的特点在于,该技术凭借拉应力作用,可以显著加快NMOS器件的电子迁移率,从而提高NMOS器件的驱动电流;然而,SMT在集成电路制造技术中如同一个“隐形人”,在整个工艺流程完成之后,该项技术不会对器件产生任何结构性的变化。

简介应力记忆技术是一种应用于NFET,NMOS等中的局部应力引入技术,可以有效提高电子输运性能,降低漏电流。应力记忆技术属于半导体工业应变工程的一种技术手段。该方法可以在半导体器件中引入应力,从而改变半导体中能带结构,以及电子输运性能。

这种方法主要包括以下几个步骤:多晶硅无定型化,沉积具有拉伸应力的衬层,快速退火,衬层移除。虽然拉伸层移除,但是通过退火过程,应力被记忆下来,从而移除衬层之后沟道仍保留应力。这种方法主要适用于n型半导体器件,而不适用于p型器件。1

应力记忆技术的分类在业界早期的探索中,SMT出现了许多流派:

①源、漏极离子注入完成之后,采用低应力水平的膜层(如二氧化硅)作为保护层,对多晶硅栅极进行高温退火;

②源、漏极离子注入完成之后,采用高应力水平的膜层(如高应力氮化硅)作为保护层,再对多晶硅栅极进行高温退火‘蹦;

③沉积高应力水平的膜层之后,直接做高温退火,而不采用预先的离子注入非晶化过程。

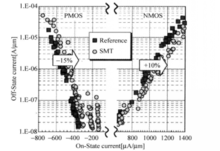

在这三大流派下面,还有很多具体的分支,诸如离子注入的条件差异、应力膜系的选择、退火条件的不同等。随着研究的逐步深入以及工业应用的反馈,上述第二种流派被越来越多的业者青睐,已经成为SMT的主流技术。而事实上,在这一分支下,仍有许多探索和实验在进行。有研究表明传统的SMT技术会降低PMOS器件的驱动电流,如下图所示。

NMOS速度可以提高10%以上,而PMOS却有15%的衰减。那么如何解决SMT的这种负面效应呢?研究者再次给出了不同的答案:比较传统的思路是,在完成高应力膜层(通常是氮化硅)沉积之后,额外增加一层光刻和刻蚀,去除PMOS区域的薄膜,再进行高温退火。但这种方法会消耗更多的制造成本,而且引入多一层光刻和刻蚀,也会给工艺控制带来更多的变异,因此有学者提出通过改善应力膜层自身特性的方法,达到既可以提高NM()S的器件速度,又不损伤PMOS性能。2

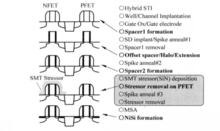

应力记忆的工艺流程由于传统SMT对于NMPS器件性能有显著提升,而对PMOS性能却有一定程度的损害。通常的思路是选择性去除PMOS区域的高应力氮化硅,,具体工艺流程如下图所示

SMT实际上是在侧墙(spacer)和白对准硅化物(salicidc)之间安插进去的一段独立的了艺,在做完侧墙之后,通常会对源、漏极进行非晶化的离子注入,生长完一层很薄的二氧化硅缓冲层之后,会在整个晶片上沉积一层高应力氮化硅。然后通过一次光刻和干法刻蚀的工艺,去除掉PMOS区域的氮化硅,通过酸槽洗掉露出来的二氧化硅,接下来就是非常关键的高温退火过程了。因为温度预算的限制,通常会采用快速高温退火技术,甚至是毫秒级退火。通常来讲,会在第一次尖峰退火(spike anneal)之后,用磷酸将剩余氮化硅全部去除,再做一次毫秒级退火。但也有人倾向于在两次退火都做完之后,再去除氮化硅。

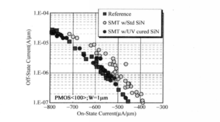

通过改善应力膜层自身特性的方法,达到既可以提高NMOS的器件速度,又不损伤PMOS性能的目的,这种方法由于可以节省一道光刻和刻蚀工艺的消耗,又被称为低成本应力记忆技术。具体下艺流程如下:在做完侧墙之后,会对源、漏极进行非晶化的离子注入,生长完一层很薄的二氧化硅缓冲层之后,再在整片晶片上沉积一层拉应力氮化硅。然后直接进行高温退火,最后才用磷酸将氮化硅一次性去除。为了减少SMT对PMOS的副作用,氮化硅沉积后加紫外光照射。紫外光照射可以减少氮化硅薄膜中的氢含量,由其引起的硼离子损失(Bloss)得到减轻,因而减少对PMOS的副作用。

总体来讲,这两种方法都有业者在使用,也各有利弊。前一种工艺更为成熟,工艺整合风险低,但存在成本高,工艺复杂的缺点;后一种工艺的优点是丁序简单,成本更低,但对氮化硅薄膜的工艺要求较高,工艺整合的可靠性还有待时间的验证。2

本词条内容贡献者为:

宋春霖 - 副教授 - 江南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国