介质隔离(Dielectric isolation)技术是集成电路制造中的一种隔离元器件的方法。集成电路是由许多元器件构成的,各个元器件之间往往需要进行电绝缘体—隔离。常用的隔离技术有pn结隔离和介质隔离等。介质隔离是采用SiO2膜来实现隔离的,漏电小、耐压高,性能优良,但是工艺比较复杂。

简介采用绝缘性能好的电介质来消除各电子元件之间的相互影响的工艺方法称为介质隔离技术。这种隔离方法的优点是各元件之间的漏电流和隔离区分布电容比P-N结隔离要小得多。它适于在高频线性放大集成电路和高速数字集成电路中使用。但由于电介质的导热性能较差,所以它在大功率集成电路中使用时,散热能力比P-N结隔离法差。1

隔离技术在功率集成电路中,各器件做在同一个硅衬底上,由于硅衬底是导电的,为了避免各器件之间的相互影响,必须进行电隔离。并且,高压晶体管与低压晶体管之间的电隔离尤为重要。

如下图所示,如果在n-衬底上有一个高压npn晶体管和一个低压pMOS管,若两者之间不隔离,不仅会产生一个微小的漏电流使功耗增加,而且栅氧化层(约lOOnm)很难承受pMOS栅极与衬底之间跨接的高电压,因此两者之间必须加以隔离。

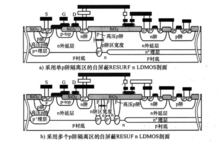

PIC介质隔离技术PIC中的介质隔离与VLIC中的基本相同,并可以利用介质隔离来改善器件的特性。如图中a所示,采用常规的介质隔离,由于VDMOS的n-漂移区较厚,载流子在源、漏区之间传输时经历的路径较长,导致其导通电阻增大,漏极电流减小。如图中b所示,若在底部增加V形槽后,可以缩短源、漏之间的距离,减小了n-漂移区的电阻,有利于提高电流密度,而且当A处源、漏之间的长度等于或大于B处源、漏之间的长度时,V形槽的引入不会影响其击穿电压。这种介质隔离可以通过调整刻蚀窗口的大小,利用离子注入形成n+漏区,通过热生长形成隔离SiO2氧化层,之后可按照常规的介质隔离工艺来实现。

采用介质隔离,器件之间绝缘隔离性能好,没有漏电流,不会发生相互干扰和闩锁现象。与结隔离相比,介质隔离区宽度可以做得很小,有利于减小芯片面积;由于SiO2绝缘性能好,故隔离电压可高达lkV,且高温漏电流小,但介质隔离的工艺比较复杂。2

本词条内容贡献者为:

王沛 - 副教授、副研究员 - 中国科学院工程热物理研究所

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国