逻辑接口指能够实现数据交换功能但物理上不存在,需要通过配置建立的接口,包括Dialer(拨号)接口、子接口、LoopBack接口、NULL接口、备份中心逻辑通道以及虚拟模板接口等。

简介逻辑接口是相对于物理接口的而言的,而物理接口就是通常所说的硬件接口,比如usb口,而逻辑接口就是程序中预留的接口。逻辑接口指能够实现数据交换功能但物理上不存在,需要通过配置建立的接口,包括Dialer(拨号)接口、子接口、LoopBack接口、NULL接口、备份中心逻辑通道以及虚拟模板接口等。

路由器逻辑接口Dialer接口Dialer接口即拨号接口。Dialer口下建立拨号规则,物理口引用一个(轮询DCC,最常用)或多个(共享DCC,极少使用)Dialer口的规则,配置方便,维护简单.

MFR接口MFR(MultilinkFrameRelay)接口是多链路帧中继接口,多个物理接口可以同一个MFR接口捆绑起来,从而形成一个拥有大带宽的MFR接口.当将帧中继物理接口捆绑进MFR接口之后,其上配置的网络层参数和帧中继链路层参数将不再起作用.在MFR接口上可以配置IP地址等网络层参数和DLCI等帧中继参数,捆绑在MFR接口内的物理接口都将使用此MFR接口的参数.

LoopBack接口TCP/IP协议规定,127.0.0.0网段的地址属于环回地址。包含这类地址的接口属于环回接口。在华为系列路由器上,定义了接口LoopBack为环回接口,可以用来接收所有发送给本机的数据包。这类接口上的地址是不可以配置的并且也不通过路由协议对外发布的。

有些应用(比如配置SNA的Localpeer)需要在不影响物理接口配置的情况下,配置一个带有指定IP地址的本地接口,并且出于节约IP地址的需要,需要配置32位掩码的IP地址,并且需要将这个接口上的地址通过路由协议发布出去。Loopback接口就是为了满足这种需要而设计的.

主要用途如下:

1、做管理IP地址

2、做OSPF协议的routerid

3、SNA,哑终端中用来捆绑源地址

4、BGP中作为建立TCP邻居的源地址

5、测试

NULL接口Null接口是一种纯软件性质的逻辑接口,任何送到该接口的网络数据报文都会被丢弃,主要用于配置黑洞路由子接口

VRP中提出了子接口的概念,所谓子接口就是在一个物理接口上配置出来的多个逻辑上的虚接口,这些虚接口共用物理接口的物理层参数,又可以分别配置各自的链路层和网络层参数.因这样的多个虚接口可以对应一个物理接口,故常被称为“子接口”。

备份中心逻辑通道备份中心不公提供各接口之间的互相备份,也允许将X.25帧中继等类型的一条虚电路作为备份中心的主接口或备份接口。

为了配置方便,用户可以对上述虚电路指定相应的逻辑通道,并在逻辑通道中配置备份中心的工作参数.1

常用单端逻辑接口电平标准单端接口具有易于设计和使用的优点,在低于300MHz的场合,单端接口被广泛使用。

TTL和CMOSTTL即Transistor—TransistorLogic,三极管结构,5V供电;CMOS即Com—plementaryMetalOxideSemiconduc—tor,是电压型器件,相对TTL有更大的噪声容限,输入阻抗大,5V供电。以前常用的74xx和4000系列器件采用的就分别是TTL和CM0S电平逻辑,目前已较少使用。2

LVTTL和LVCMOS随着技术和工艺的发展以及设备低功耗等要求,供电电压越来越低,LVTTL和LVCOMS分别在TTL和CMOS的基础上发展起来。LVTTL和LVCMOS常用的供电电压有3.3V、2.5V、1.8V。LVTTLL和LVCMOS驱动和接收器通常是简单的对称上下拉结构,只要满足Vi和Vo的高低电平标准和驱动电流范围,二者就可以相互转化。图1(a、b)为LVTTL的输入电路

和输出缓中器结构,表1和表2分别为LVTTL和LVCMOS的输入、输出电压和电流规范。2

SSTLSSTL即StubSeriesTerminatedLogic标准,分为SSTL_3、SSTL_2、SSTL_18三种,对应不同的供电电压,它与LVTTL和LVCMOS的不同在于SSTL是传输线终端匹配的,因此SSTL具有输器,一般有VCCO=1.8V和VCCO=1.5V两种标准。HSTL和SSTL对参考电平要求均比较高(1%精度)。2

常用差分逻辑接口电平标准差分信号较单端信号能够以低电压摆幅提供更大的电压增益和带宽,同时还可以去除共模和偶次谐波的干扰,从而提供更高的数据传输率。其缺点是差分信号增加了信号管脚,在PCB布线时应考虑阻抗、间距、长度等的匹配。随着高速实时性数据传输的要求越来越高,差分信号应用越来越广,下面介绍三种最常见的差分逻辑接口标准。2

CMLCML电平是所有高速数据接口中最简单的一种。其输入和输出都是匹配好的,减少了外围器件,适合于更高频段工作。

CML的输入、输出缓冲电路如图,R1和R2是为了限制电流,通常数值相等,为50Ω。 由图可以看出,该电路是差分对形式。该差分对的集电极电阻为50Q,输出信号的高低电平切换是靠共发射极差分对的开关控制的。差分对的发射极到地的恒流源典型值为16mAf图3中的电流源I1),假定CML的输出负载为一个50Q上拉电阻,则单端CML输出信号的摆幅为Vcc~Vcc一0.4V,改变l1的数值则改变了电压的摆幅。

由图可以看出,该电路是差分对形式。该差分对的集电极电阻为50Q,输出信号的高低电平切换是靠共发射极差分对的开关控制的。差分对的发射极到地的恒流源典型值为16mAf图3中的电流源I1),假定CML的输出负载为一个50Q上拉电阻,则单端CML输出信号的摆幅为Vcc~Vcc一0.4V,改变l1的数值则改变了电压的摆幅。

CML到CML之间的连接分两种情况:当收发两端的器件使用相同的电源时,CML到CML可以采用直流耦合方式,不用加任何器件;当收发两端器件采用不同电源时,一般要考虑交流耦合,中间加耦合电容(注意这时选用的耦合电容要足够大,以避免在较长连0或连1情况出现时,接收端差分电压变小)。CML也有不足,即由于自身驱动能力有限,CML更适于芯片间较短距离的连接,而且不同用户间CML接口实现方式差异较大,所以现有器件提供CML接口的数目还不是非常多。2

ECL、PECL和LVPECLECL(EmitterCoupledLogic)即射极耦合逻辑,是带有射随输出结构的典型输入、输出接口电路,ECL电路的最大特点是其基本门电路工作在非饱和状态,正因为如此,ECL电路的最大优点是具有相当高的速度,平均延迟时间可达ns数量级甚至更少。

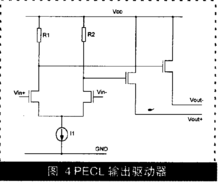

传统的ECL以Vcc为零电压,VEE为-5.2V电源,Vo=Vcc-0.9V=-0.9V,VOL=Vcc-1.7V=-1.7V,所以ECL电路的逻辑摆幅较小(仅约0.8V)。当电路从一种状态过渡到另一种状态时,对寄生电容的充放电时间将减少,这也是ECL电路具有高开关速度的重要原因。另外,ECL电路是由一个差分对管和一对射随器组成的,如图4所示,所以输入阻抗大,输出阻抗小,驱动能力强,信号检测能力高,差分输出,抗共模干扰能力强;但是由于单元门的开关管对是轮流导通的,对整个电路来讲没有“截止”状态,所以电路的功耗较大。

传统的ECL以Vcc为零电压,VEE为-5.2V电源,Vo=Vcc-0.9V=-0.9V,VOL=Vcc-1.7V=-1.7V,所以ECL电路的逻辑摆幅较小(仅约0.8V)。当电路从一种状态过渡到另一种状态时,对寄生电容的充放电时间将减少,这也是ECL电路具有高开关速度的重要原因。另外,ECL电路是由一个差分对管和一对射随器组成的,如图4所示,所以输入阻抗大,输出阻抗小,驱动能力强,信号检测能力高,差分输出,抗共模干扰能力强;但是由于单元门的开关管对是轮流导通的,对整个电路来讲没有“截止”状态,所以电路的功耗较大。

PECL(PositiveEmitterCoupledLogic)将ECL电路中的负电源改用正电源(+5V),可将Vcc接到正电源而VEE接到零点。如果采用+3.3V供电,则称为LVPECL。由图可以看出,PECL是开路输出,所以需用下拉电阻到地。不过同CML一样,LVPECL输出高低电平的摆幅因制造商不同而不同,它不仅与外部电阻有关,与逻辑门的VDD也有关。2

LVDS即低电压差分信号,的驱动器由驱动差分线对的电流源组成,如图所示,电流通常为3.5mA。接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过的100Ω匹配电阻,并在接收器的输入端产生大350mV约的电压。当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。2

本词条内容贡献者为:

李岳阳 - 副教授 - 江南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国