简介特定处理任务

例如,数学协处理器可以控制数字处理;图形协处理器可以处理视频绘制。例如,intel pentium 微处理器就包括内置的数学协处理器。

内核相连协处理器可以附属于ARM处理器。一个协处理器通过扩展指令集或提供配置寄存器来扩展内核处理功能。一个或多个协处理器可以通过协处理器接口与ARM内核相连1。

协处理器可以通过一组专门的、提供load-store类型接口的ARM指令来访问。例如协处理器15(CP15),ARM处理器使用协处理器15的寄存器来控制cache、TCM和存储器管理。

扩展指令集协处理器也能通过提供一组专门的新指令来扩展指令集。例如,有一组专门的指令可以添加到标准ARM指令集中,以处理向量浮点(VFP)运算。

这些新指令是在ARM流水线的译码阶段被处理的。如果在译码阶段发现是一条协处理器指令,则把它送给相应的协处理器。如果该协处理器不存在,或不认识这条指令,则ARM认为发生了未定义指令异常。这也使得编程者可以用软件来仿真协处理器的行为(使用未定义指令异常服务子程序)。

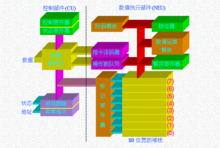

内部结构协处理器80x87的内部结构如图所示。它可分为二个主要部分:控制部件(CU)和数值执行部件(NEU)。

控制部件(CU)把协处理器接到CPU的系统总线上,协处理器和CPU都监视正在执行的指令流。如果当前将要执行的指令是协处理器指令(即:ESCape指令),那么,协处理器会自动执行它,否则,该指令将交给CPU来执行。

数值执行部件(NEU)复制执行所有的协处理器指令,它有一个用8个80位的寄存器组成的堆栈,该堆栈用于以扩展精度的浮点数据格式来存放数学指令的操作数和运算结果。在协处理器指令的执行过程中,要么指定该堆栈寄存器中的数据,要么使用压栈/出栈机制来从栈顶存放或读取数据。

在NEU部件中,还有一些记录协处理器工作状态的寄存器,如:状态寄存器、控制寄存器、标记寄存器和异常指针寄存器等。有关这些寄存器的作用将在后面给予分别介绍。

现代PC协处理器2006年,AGEIA宣布了PhysX物理加速卡, PhysX被设计来处理那些耗时复杂的物理计算。2008年,Nvidia收购了AGEIA,NVIDIA将PhysX物理引擎,利用CUDA技术,由显示核心加速运算。

2008年,Khronos Group发布OpenCL,这是一个通用语言,支持ATI/AMD和Nvidia的GPU。

2012年,Intel宣布Intel Xeon Phi协处理器。

2013年,苹果在iPhone 5s上首次推出了M7运动协处理器2。

超级CPU协处理器的消亡80486CPU之前有协处理器,提高浮点运算能力,那时cpu较弱才有的协处理器,速度是原来数百倍不止,pc机一般不存在协处理器了。

ARM 微处理器ARM 微处理器可支持多达 16 个协处理器,用于各种协处理操作,在程序执行的过程中,每个协处理器只执行针对自身的协处理指令,忽略 ARM 处理器和其他协处理器的指令。ARM 的协处理器指令主要用于 ARM 处理器初始化 ARM 协处理器的数据处理操作,以及在ARM 处理器的寄存器和协处理器的寄存器之间传送数据,和在 ARM 协处理器的寄存器和存储器之间传送数据。 ARM 协处理器指令包括以下 5 条: — CDP 协处理器数操作指令— LDC 协处理器数据加载指令— STC 协处理器数据存储指令— MCR ARM 处理器寄存器到协处理器寄存器的数据传送指令— MRC 协处理器寄存器到ARM 处理器寄存器的数据传送指令。

ARM:协处理器包括以下5条:

CDP:协处理器数据操作指令。

LDC:协处理器数据加载指令。

STC:协处理器数据存储指令。

MCR:ARM处理器寄存器到协处理器寄存器的数据传送指令。

MRC:协处理器寄存器到ARM处理器寄存器的数据传送指令3。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国