简介

伪随机二进制序列,是一种可以预先确定并可以重复地产生和复制,又具有随机统计特性的二进制码序列。在现代工程实践中,伪随机信号在移动通信、导航、雷达和保密通信、通信系统性能的测量等领域中有着广泛的应用。例如,在连续波雷达中可用作测距信号,在遥控系统中可用作遥控信号,在多址通信中可用作地址信号,在数字通信中可用作群同步信号,还可用作噪声源以及在保密通信中的加密作用等。伪随机发生器在测距、通信等领域的应用日益受到人们重视。伪随机信号与随机信号的区别在于:随机信号是不可预测的。它在将来时刻的取值只能从统计意义上去描述;伪随机序列实质上不是随机的,而是收发双方都知道的确定性周期信号。之所以称其为伪随机序列,是因为它表现出白噪声采样序列的统计特性,在不知其生成方法的侦听者看来像真的随机序列一样。M序列作为一种基本的PN序列,具有很强的系统性、规律性和相关性。M序列的理论发展比较成熟。实现比较简便,利用n级移位寄存器可产生长度为2“一l的M序列。目前,3G移动通信技术仍是通信领域的研究热点,其基本特征之一就是码分多址【4l,其中的码就是PN码,PN码的选择直接影响到CDMA系统的容量、抗干扰能力、接入和切换速度等性能。因此,PN码技术作为3G移动通信系统的核心技术之一。已得到广泛的关注、研究和应用。

在通信系统中,误码测试的功能和指标是其中的重要指标之一。高速PRBS的产生与再生是高速误码分析仪中的关键技术之一。在此,结合PRBS在通信系统中误码测试方面的应用讨论由并行PRBS产生高速串行PRBS的方法1。

PRBS原理M序列的特性误码分析仪中的数码流是伪随机的。它实际上是一种M序列,即由带线性反馈的移位寄存器产生的周期最长的一种序列,它具有许多特别的性质,下面只列出与M序列的有关特性。

均衡性:在M序列的一个周期中,l和0的个数基本相等。

游程分布:一个序列中取值相同的那些相继的元素合称为一个游程。在一个游程中元素的个数称为游程长度。一般来说,在M序列中长度为k的游程占游程总数的1/2^k。若M序列的周期为2^n一l,那么,其中最长的游程只有一个,即连续n个1组成的游程是其最长的游程。

移位相加特性:一个M序列Mp与其经任意次延迟移位产生的另一不同序列Mr模2相加,得到的仍是Mp的某次延迟移位序列Ms。

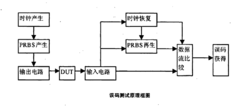

误码测试的原理图 是误码测试的原理框图。其中时钟产生、PRBS产生、输出电路等模块构成发射单元,DUT是被测电路或传输线路,输入电路、时钟恢复、PRBS再生、数据流比较、误码获得等模块构成接收单元。PRBS的产生、再生是其中的关键技术之一。

是误码测试的原理框图。其中时钟产生、PRBS产生、输出电路等模块构成发射单元,DUT是被测电路或传输线路,输入电路、时钟恢复、PRBS再生、数据流比较、误码获得等模块构成接收单元。PRBS的产生、再生是其中的关键技术之一。

并行PRBS产生的原理在高速通信系统中,由于器件速度的限制,常常需要在较低的速率(如四分之一速率)下先产生并行PRBS,然后再由并/串变换电路产生高速的PRBS。

图 是四路并行的PRBS经过并/串变换产生指定串行速率的PRBS的过程。“CLK/2”是指需要的速率(CLK)的1/2倍的时钟,“PRBS延迟1T/4”是指特定PRBS延迟1/4周期的PRBS。

是四路并行的PRBS经过并/串变换产生指定串行速率的PRBS的过程。“CLK/2”是指需要的速率(CLK)的1/2倍的时钟,“PRBS延迟1T/4”是指特定PRBS延迟1/4周期的PRBS。

四路(两两相差1/4周期的)PRBS先产生两路1/2速率的PRBS(两路相差1/2周期),再由两路相差1/2周期的PRBS产生全速率的PRBS。可见用此方法产生的PRBS,可以使其大部分电路工作在1/4速率下,在1/4速率下完成PRBS产生、误码插入、误码统计等功能;只有少数电路工作在1/2速率和全速率下。降低了对硬件的要求。

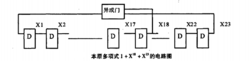

并行PRBS的实现 通信系统中使用的PRBS应符合ITU-T Rec.O.150~O.153的要求,ITU-T Rec.O.151规定周期为2^23-1的PRBS的本原多项式为1+X^18+X^23。它可以由23个D触发器加上异或门来实现,如图。

通信系统中使用的PRBS应符合ITU-T Rec.O.150~O.153的要求,ITU-T Rec.O.151规定周期为2^23-1的PRBS的本原多项式为1+X^18+X^23。它可以由23个D触发器加上异或门来实现,如图。

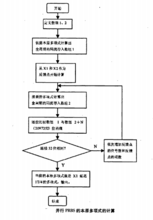

我们以周期为2^23-1的PRBS为例来说明四路并行的PRBS的实现。产生的四路并行的PRBS必须相差1/4个PRBS周期。。PRBS 2^23-1的周期为8388607位;其1/4周期为2097152位。X1定义为延迟0位的输出端。依据图 提供的流程图,可由计算机完成复杂的计算过程。设N值分别为1/4周期位(2097152位)、2/4周期位(4194304位)、3/4周期位(6291456位),则可分别计算出延迟1T/4、2T/4、3T/4的本原多项式B、C、D

提供的流程图,可由计算机完成复杂的计算过程。设N值分别为1/4周期位(2097152位)、2/4周期位(4194304位)、3/4周期位(6291456位),则可分别计算出延迟1T/4、2T/4、3T/4的本原多项式B、C、D

B=X^6+X^11+X^13+X^15+X^18+X^20

C=X^7+X^12+X^16+X^21

D=X^1+X^6+X^10+X^15+X^17+X^22.

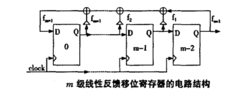

PRBS的FPGA实现图 是m级线性反馈移位寄存器的电路结构。其中系数因子fi=1表示有连接,fi=0表示无连接;⊕表示异或(XOR)运算。显然,线性反馈移位寄存器的输出序列是有周期性的。因为一旦m个寄存器上出现了以前经历过的状态,则此后的状态将周而复始。m级的线性反馈移位寄存器最多只有2m个状态,所以重复是不可避免的。假若优个寄存器的初始状态全为零,则线性反馈移位寄存器将一直保持全零状态。因此,在初始状态非全零的前提下,线性反馈移位寄存器的周期r≤2m-1。如果选取适当的反馈方式。m级线性反馈移位寄存器所产生的序列周期可以达到最大值2m-1,这时线性反馈移位寄存器所产生的伪随机序列也称为最长序列(或者m序列)。线性反馈移位寄存器的周期只与其反馈方式有关,而不依赖于其初始状态。根据其反馈方式的不同,可以定义线性反馈移位寄存器的特征多项式为:

是m级线性反馈移位寄存器的电路结构。其中系数因子fi=1表示有连接,fi=0表示无连接;⊕表示异或(XOR)运算。显然,线性反馈移位寄存器的输出序列是有周期性的。因为一旦m个寄存器上出现了以前经历过的状态,则此后的状态将周而复始。m级的线性反馈移位寄存器最多只有2m个状态,所以重复是不可避免的。假若优个寄存器的初始状态全为零,则线性反馈移位寄存器将一直保持全零状态。因此,在初始状态非全零的前提下,线性反馈移位寄存器的周期r≤2m-1。如果选取适当的反馈方式。m级线性反馈移位寄存器所产生的序列周期可以达到最大值2m-1,这时线性反馈移位寄存器所产生的伪随机序列也称为最长序列(或者m序列)。线性反馈移位寄存器的周期只与其反馈方式有关,而不依赖于其初始状态。根据其反馈方式的不同,可以定义线性反馈移位寄存器的特征多项式为:

在不同应用场合下,对线性反馈移位寄存器所产生的随机序列的周期长度有不同要求。随着m的增大,线性反馈移位寄存器对FPGA内部逻辑资源的消耗量线性增加,而线性反馈移位寄存器输出的最长序列周期却呈指数增长,这一点对实际应用来说是非常有利的。当m=63时。最大长度序列的周期可达9.22337×10^18如果CLK频率为50MHz,则重复周期超过5800年。在大多实际应用中,这样的序列长度是非常充裕的2。

PRBS发送

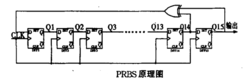

利用线性反馈移位寄存器产生PRBS可以有很多种生成多项式,其中应用最广泛的是PRBSl5序列。PRBS-15的生成多项式是:X^15+X^14+1;PRBS的生成采用FPGA内部的D触发器(DFF)实现起来非常简单。PRBS-15序列产生电路实现原理如图 所示。

所示。

PRBS检测

接收端的PRBS检测有两种常用的方式,分别是图案检测和公式检测法。

1、图案检测

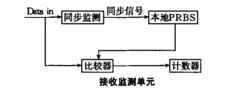

这种方法的方案是:在接收端同样有一个相同的PRBS/PRss生成器,把接收到的数字序列与本地产生器输出的码型进行比较,从而得到误码的结果。在进行比较前,必须使本地的产生器要与发送端的生成器达到同步。达到同步的原理与帧定位系统原理相似,但与后者相比要简单的多。伪随机序列是按一定规律(周期)产生和复制而成,所以序列的生成也存在着一定的周期,把每一周期的序列看成一个帧,由它生成的原理可知在这一周期内,每一组15位长度的码型都是唯一存在的,可以把这15位码型看成帧定位信号处理,从而能达到同步,只是不需要校核/保护逻辑。同步信号再控制本地生成器。原理如图。

这种方法的方案是:在接收端同样有一个相同的PRBS/PRss生成器,把接收到的数字序列与本地产生器输出的码型进行比较,从而得到误码的结果。在进行比较前,必须使本地的产生器要与发送端的生成器达到同步。达到同步的原理与帧定位系统原理相似,但与后者相比要简单的多。伪随机序列是按一定规律(周期)产生和复制而成,所以序列的生成也存在着一定的周期,把每一周期的序列看成一个帧,由它生成的原理可知在这一周期内,每一组15位长度的码型都是唯一存在的,可以把这15位码型看成帧定位信号处理,从而能达到同步,只是不需要校核/保护逻辑。同步信号再控制本地生成器。原理如图。

图中,从远端接收到PRBS。首先进行数据监测,监测到预设的数字则启动本地麟产生器,这样使接收的序列与本地的序列达到完全同步,从而便于比较,比较器是一个简单的异或门,当两序列数据不同时比较器输出高电平,当相同时则为低电平。当输出高电平则启动计数器。从而计数器累加误码个数。CPU定时访问计数寄存器,访问后计数器清零,CPU将会计算误码率。

2、公式计算法

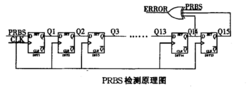

PRBS都是按照一定的公式生成的,所以在接收端只要验证接收到的数字序列是否能够满足公式从而判断出是否误码。PRBS公式验证原理如图所示。在这种方法中有一个现象没有考虑到,接收来的信号全0’的情况,全‘0’情况可以验证也满足了上图,所以如果Q1、Q2、……Q15同时为0时,error也要输出高电平。如图

PRBS都是按照一定的公式生成的,所以在接收端只要验证接收到的数字序列是否能够满足公式从而判断出是否误码。PRBS公式验证原理如图所示。在这种方法中有一个现象没有考虑到,接收来的信号全0’的情况,全‘0’情况可以验证也满足了上图,所以如果Q1、Q2、……Q15同时为0时,error也要输出高电平。如图 ,从远端接收到PRBS送入到PRBs监测端。检测来到的数据是否符合PRBS产生的公式,如不符合则输出脉冲送到计数器中。

,从远端接收到PRBS送入到PRBs监测端。检测来到的数据是否符合PRBS产生的公式,如不符合则输出脉冲送到计数器中。

3、两种方法的比较

在前一种设计中,需要同步电路与PRBS生成器,所以它需要一段时间的同步而且资源也比较浪费,但是一旦达到同步后检测的准确性比较高。而后一种的方法直接应用PRBS产生器的数学公式,它的同步速度快而且实现也比较简单,节省资源。但是由检测原理图看出如果序列中出现一个比特的误码,它将会影响到对随后序列的判断,所以用这种方法检测出的误码数偏高。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国