近日,我校合肥微尺度物质科学国家研究中心曾华凌教授、物理学院乔振华教授和化学与材料科学学院邵翔教授在二维电学器件范德华接触研究中取得新进展,展示了一种制备二维电学器件的“全堆叠”技术,优化了二维材料与金属电极之间的界面接触,为二维电学器件的制备提供了一种高效、高质量且高稳定性的普适方法。相关研究成果于5月30日以“Reliable wafer-scale integration of two-dimensional materials and metal electrodes with van der Waals contacts”为题在线发表在国际学术期刊《自然·通讯》上(Nat. Commun.15:4619(2024))。

在二维电学器件制备的常规工艺中,金属电极的蒸镀是一个关键环节。蒸发的高能量金属原子在沉积到二维材料表面的过程中极易造成其晶格损伤,从而引入大量缺陷,在影响电极/二维材料界面电学接触的同时,导致严重的费米钉扎效应,最终影响器件的电学性能。因此,实现二维材料和金属电极间的可靠电学接触成为了改善二维电学器件性能的关键问题。近年来的研究表明,对于二维电学器件,边缘接触是一种理想的电学接触模式,但其技术难度较大,难以规模化应用。相比之下,在二维材料表面实现范德华接触可能是一种更好的选择。范德华接触是指二维材料和金属电极通过范德华力相作用,这种方式在避免引入大量缺陷的同时能够实现较好的电学接触,具有更强的操作性和大规模应用的潜力。

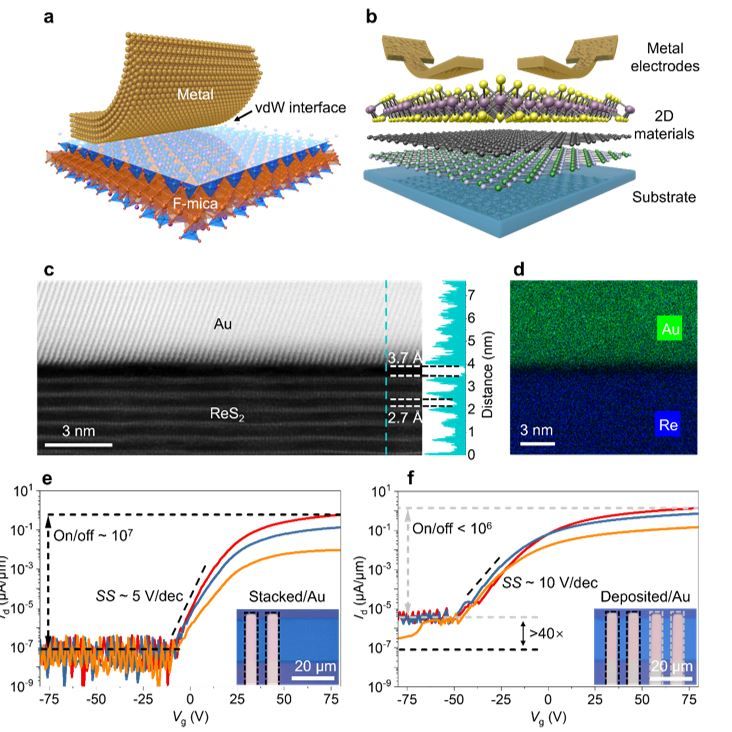

为了实现可靠的二维范德华接触,该团队开发了一种“全堆叠”技术,在二维电学器件的制备过程中,实现金属电极与二维材料的直接堆叠,避免了金属蒸镀等环节,从而保护了二维材料免受损伤,并实现了优良的电学性能。如图1所示,利用全堆叠技术制备的二维电学器件具有锐利的金属-半导体接触界面,界面处存在平整、清晰的范德华间隙,并且二维材料一侧没有金属原子的掺杂,这表明金属电极和二维半导体之间形成了高质量的范德华接触。由于接触界面的改善,全堆叠技术制备的二维半导体晶体管相比于金属蒸镀工艺,关态电流降低了95%以上,亚阈值摆幅降低了50%,同时具备更高的开关比,在实现低功耗集成电路方面更具优势。

图1. 全堆叠技术及制备的二维电学器件。(a-b)范德华衬底辅助的金属电极剥离及全堆叠技术示意图;(c-d)全堆叠技术制备的二维电学器件截面原子图像及元素分布,展示了金属- 二维半导体间锐利的范德华界面(3.7 Å);(e-f)全堆叠技术制备的二维场效应晶体管电学性能,其开关比高达107,亚阈值摆幅约5 V/dec,比利用蒸镀电极制备的晶体管器件性能提升一个数量级。

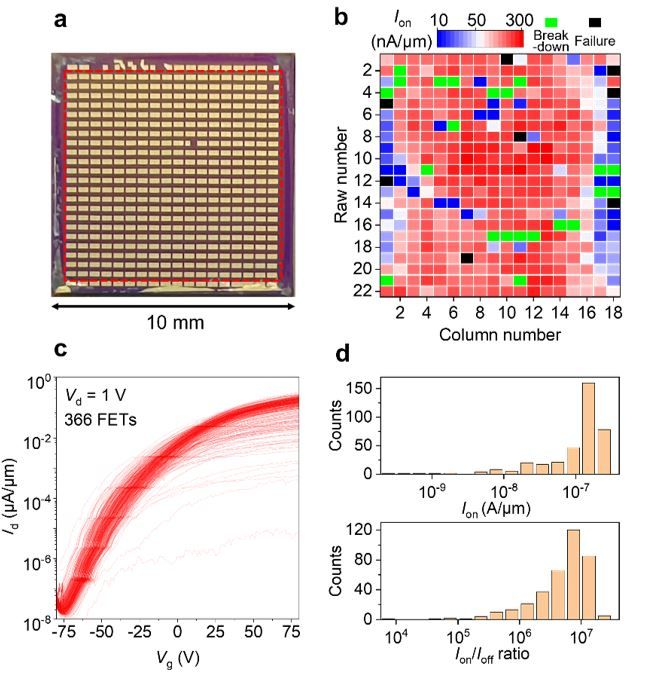

为了展示全堆叠技术在晶圆级制造上的潜力,团队利用该技术制备了单层二硫化钼的场效应晶体管阵列(如图2所示),器件良率高达98.4%,表现出优异的一致性和稳定性。这一晶体管阵列的平均开关比为6.8×106,其中开关比大于106的器件占比达91.3%。晶体管阵列的优良性能和高度一致性进一步证明了全堆叠技术在实现二维电学器件可靠电学接触方面的优势,表明该技术有望为未来二维电学器件的工业级制造提供新的技术路径。

图2. 单层二硫化钼场效应晶体管阵列制备及电学性能。 ( a )全堆叠技术制备的单层MoS2场效应晶体管阵列;( b )396个单层MoS2晶体管的开态电流分布统计;( c-d )366个单层MoS2晶体管的转移特性曲线及开态电流、开关比统计分布(排除击穿及损坏器件)。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国