Verilog模型可以是实际电路不同级别的抽象,因此有多种不同的建模方法。结构化的建模方式就是通过对电路结构的描述来建模,即通过对器件的调用,并使用线网来连接各器件的描述方式。结构化的描述方式反映了一个设计的层次结构。

Verilog HDL建模概述在数字电路设计中,数字电路可简单归纳为两种要素:线和器件。线是器件管脚之间的物理连线;器件也可简单归纳为组合逻辑器件(如与或非门等)和时序逻辑器件(如寄存器、锁存器、RAM等)。一个数字系统(硬件)就是多个器件通过一定的连线关系组合在一块的。因此,Verilog HDL的建模实际上就是如何使用HDL语言对数字电路的两种基本要素的特性及相互之间的关系进行描述的过程。1

简介Verilog模型可以是实际电路不同级别的抽象,因此有多种不同的建模方法。其中最常用的建模方法有以下三种:

1)门级结构建模

2)行为描述建模

3)数据流建模

结构化的建模方式就是通过对电路结构的描述来建模,即通过对器件的调用(HDL概念称为例化),并使用线网来连接各器件的描述方式。这里的器件包括Verilog HDL的内置门如与门and,异或门xor等,也可以是用户的一个设计。结构化的描述方式反映了一个设计的层次结构。

在实际应用中,实例化语句主用指后者,对内置门建议不采纳,而用数据流或行为级方式对基本门电路的描述。端口队列port_list列出了该模块通过哪些端口与外部模块通信。1

建模示例对一个数字系统的设计,我们采用的是自顶向下的设计方式。可把系统划分成几个功能模块,每个功能模块再划分成下一层的子模块。每个模块的设计对应一个module,一个module设计成一个verilog HDL程序文件。因此,对一个系统的顶层模块,可采用结构化的设计,即顶层模块分别调用了各个功能模块。

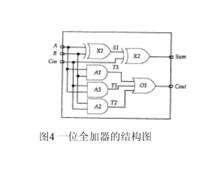

一位全加器代码:

module FA_struct (A, B, Cin, Sum, Count);input A;input B;input Cin;output Sum;output Count;wire S1, T1, T2, T3;// -- statements -- //xor x1 (S1, A, B);xor x2 (Sum, S1, Cin);and A1 (T3, A, B );and A2 (T2, B, Cin);and A3 (T1, A, Cin);or O1 (Cout, T1, T2, T3 );endmodule该实例显示了一个全加器由两个异或门、三个与门、一个或门构成。S1、T1、T2、T3则是

门与门之间的连线。代码显示了用纯结构的建模方式,其中xor、and、or是Verilog HDL内置的门器件。以xor x1 (S1, A, B)该例化语句为例:

xor表明调用一个内置的异或门,器件名称xor,代码实例化名x1(类似原理图输入方式)。括号内的S1,A,B表明该器件管脚的实际连接线(信号)的名称,其中A、B是输入,S1是输出。其他同。1

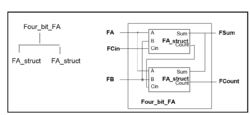

两位的全加器两位的全加器可通过调用两个一位的全加器来实现。该设计的设计层次示意图和结构图如下:

代码:

module Four_bit_FA (FA, FB, FCin, FSum, FCout ) ;parameter SIZE = 2;input [SIZE:1] FA;input [SIZE:1] FB;input FCin;output [SIZE:1] FSum;output FCout;wire FTemp;FA_struct FA1(.A (FA[1]),.B (FB[1]),.Cin (FCin) ,.Sum (FSum[1]),.Cout (Ftemp));FA_struct FA2(.A (FA[2]),.B (FB[2]),.Cin (FTemp) ,.Sum (FSum[2]),.Cout (FCount ));endmodule该实例用结构化建模方式进行一个两位的全加器的设计,顶层模块Four_bit_FA调用了两个一位的全加器FA_struct。在这里,以前的设计模块FA_struct对顶层而言是一个现成的器件,顶层模块只要进行例化就可以了。

注意这里的例化中,端口映射(管脚的连线)采用名字关联,如.A(FA[2]),其中.A表示调用器件的管脚A,括号中的信号表示接到该管脚A的电路中的具体信号。wire保留字表明信号Ftemp是属线网类型)。

另外,在设计中,尽量考虑参数化的问题。器件的端口映射必须采用名字关联。1

本词条内容贡献者为:

何星 - 副教授 - 上海交通大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国