存储层次是在计算机体系结构下存储系统层次结构的排列顺序。每一层于下一层相比都拥有较高的速度和较低延迟性,以及较小的容量。大部分现今的中央处理器的速度都非常的快。大部分程序工作量需要存储器访问。由于高速缓存的效率和存储器传输位于层次结构中的不同档次,所以实际上会限制处理的速度,导致中央处理器花费大量的时间等待存储器I/O完成工作。

简介存储系统是指计算机中由存放程序和数据的各种存储设备、控制部件及管理信息调度的设备(硬件)和算法(软件)所组成的系统。计算机的主存储器不能同时满足存取速度快、存储容量大和成本低的要求,在计算机中必须有速度由慢到快、容量由大到小的多级层次存储器,以最优的控制调度算法和合理的成本,构成具有性能可接受的存储系统。存储系统的性能在计算机中的地位日趋重要,主要原因是:①冯诺伊曼体系结构是建筑在存储程序概念的基础上,访存操作约占中央处理器(CPU)时间的70%左右。②存储管理与组织的好坏影响到整机效率。③现代的信息处理,如图像处理、数据库、知识库、语音识别、多媒体等对存储系统的要求很高1。

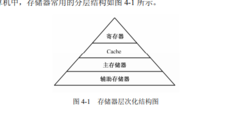

对于通用计算机而言,存储层次分为四层:CPU寄存器。高速缓存、主存和辅存。对于CPU 寄存器,CPU 可以再一个时钟周期内访问它们。接下来是一个或者多个小型到中型的基于 SRAM 的高速缓存存储器,可以再几个 CPU 时钟周期内访问它们。然后是一个大的基于 DRAM 的主存,可以在几十或者几百个时钟周期内访问它们。接下来是慢速但是容量很大的本地磁盘。存储器层次结构的核心是,对于每个 k,位于 k 层的更快更小的存储设备作为位于 k+1 层的更大更慢的存储设备的缓存。也就是说,层次结构中的每一层都缓存来自较低一层的数据对象。例如,本地磁盘作为通过网络从远程磁盘取出文件的缓存,以此类推知道 CPU 寄存器。

对于计算机系统中配置的存储器,归结起来有三个主要的参数要求:容量大,速度快,价格低。存储器的易失性也是计算机存储器的一个重要指标,一般来讲,速度高的存储器,每位价格也高,因此容量不能太大。所以对单一的存储器部件来说,大容量、高速度、低价格三者是不能同时满足的。为了解决这个难题,在现代计算机系统中采用了存储器分层结构,这样就不会仅仅依赖于某一个存储部件或技术了。任意高速存储设备都可以作为低速存储设备的缓存,也是出现存储层次主要原因之一。

特点在存储层次中,存储系统的基本要求是存储容量大、存取速度快和成本低。为同时满足上述三个要求,计算机需有速度由慢到快,容量由大到小的多层次存储器,以最优的控制调度算法和合理的成本,构成存储系统。

在图1中,存储层次由上到下呈现出以下特点:每位的价格越来越低,速度越来越慢,容量越来越大,CPU 访问的频度也越来越少。最上层的寄存器通常都制作在 CPU 芯片内,寄存器中的数直接在 CPU 内部参与运算。现代 CPU 内可以有十几个、几十个寄存器,它们的速度最快、位价(平均每位的价格)最高、容量最小。主存用 来存放将要参与运行的程序和数据,但其速度与 CPU 速度差距较大,为了使它们之间的速度更匹配,在主存与 CPU 之间插入了一种比主存速度更快、容量更小的高速缓冲存储器 (cache)。主存与缓存之间的数据调动是由硬件自动完成的,对程序员来说是透明的。这三层都在主机内,多由各种半导体存储材料制成。辅助存储器存储容量比主存储器大得多,主要用来存放暂时未用到的程序和数据文件。CPU 不能直接访问辅存,辅存只能与主存交换信息,但它的位价是最便宜的。存储器的层次结构实质上还是体现为缓存—主存和主存—辅存这两个存储层次上。从CPU 的角度看,缓存—主存层次的速度接近于缓存,容量与每位价格则接近于主存。因此,解决了速度与成本之间的矛盾。而主存—辅存这一层次,从整体分析,其速度接近于主存,容量接近于辅存,平均位价也接近于低速、廉价的辅存位价,这又解决了速度、容量、成本这三者间的矛盾。这种多层次结构已成为现代计算机的典型存储结构。在主存—辅存这一层次的发展中,形成了虚拟存储系统。在这个系统中,程序员编程的地址范围与虚拟存储器的地址空间相对应。例如,机器指令地址码为 32 位,则虚拟存储器的存储单元可达 4GB。可是这个数与主存的实际存储单元个数相比,要大得多。通常称这类指令地址码为虚地址或叫逻辑地址,而把主存的实际地址称作实地址或物理地址。物理地址是程序在执行过程中能够真正访问的地址,也是真实存在于主存的存储地址。对具有虚拟存储器的计算机系统而言,编程时可用的地址空间远远大于主存空间,使程序员以为自己占有一个容量极大的主存,其实这个主存并不存在,这就是将其称为虚拟存储器的原因。对虚拟存储器而言,其逻辑地址变换为物理地址的工作,是由计算机系统的硬件设备和操作系统自动完成的,对应用程序员是透明的。当虚地址的内容在主存储器中时,机器便可立即使用;若虚地址的内容不在主存,则必须先将此虚地址的内容在辅存中找到,传递到主存储器的合适单元后再被机器所用。主存储器是可以和 CPU 直接交换信息的存储器,它通常由存放程序和数据的随机读写存储器 RAM 和存放某些固定内容的只读存储器 ROM组成。

来存放将要参与运行的程序和数据,但其速度与 CPU 速度差距较大,为了使它们之间的速度更匹配,在主存与 CPU 之间插入了一种比主存速度更快、容量更小的高速缓冲存储器 (cache)。主存与缓存之间的数据调动是由硬件自动完成的,对程序员来说是透明的。这三层都在主机内,多由各种半导体存储材料制成。辅助存储器存储容量比主存储器大得多,主要用来存放暂时未用到的程序和数据文件。CPU 不能直接访问辅存,辅存只能与主存交换信息,但它的位价是最便宜的。存储器的层次结构实质上还是体现为缓存—主存和主存—辅存这两个存储层次上。从CPU 的角度看,缓存—主存层次的速度接近于缓存,容量与每位价格则接近于主存。因此,解决了速度与成本之间的矛盾。而主存—辅存这一层次,从整体分析,其速度接近于主存,容量接近于辅存,平均位价也接近于低速、廉价的辅存位价,这又解决了速度、容量、成本这三者间的矛盾。这种多层次结构已成为现代计算机的典型存储结构。在主存—辅存这一层次的发展中,形成了虚拟存储系统。在这个系统中,程序员编程的地址范围与虚拟存储器的地址空间相对应。例如,机器指令地址码为 32 位,则虚拟存储器的存储单元可达 4GB。可是这个数与主存的实际存储单元个数相比,要大得多。通常称这类指令地址码为虚地址或叫逻辑地址,而把主存的实际地址称作实地址或物理地址。物理地址是程序在执行过程中能够真正访问的地址,也是真实存在于主存的存储地址。对具有虚拟存储器的计算机系统而言,编程时可用的地址空间远远大于主存空间,使程序员以为自己占有一个容量极大的主存,其实这个主存并不存在,这就是将其称为虚拟存储器的原因。对虚拟存储器而言,其逻辑地址变换为物理地址的工作,是由计算机系统的硬件设备和操作系统自动完成的,对应用程序员是透明的。当虚地址的内容在主存储器中时,机器便可立即使用;若虚地址的内容不在主存,则必须先将此虚地址的内容在辅存中找到,传递到主存储器的合适单元后再被机器所用。主存储器是可以和 CPU 直接交换信息的存储器,它通常由存放程序和数据的随机读写存储器 RAM 和存放某些固定内容的只读存储器 ROM组成。

存储器性能存储器性能的主要技术指标为容量、速度和易失性。

存储器既然是用来存储程序和数据的容器,当然容量是关键性的特征。计算机可寻址的最小信息单位是一个存储字,相邻的存储器地址表示相邻存储字,这种机器称为“字可寻址”机器。一个存储字所包括的二进制位数称为存储字长。一个字又可划分为若干个“字节”,一个字节为 8 个二进制位,因此,一个字的字长通常是 8 的倍数。有些计算机也可以按“字节”寻址,因此,这种机器称为“字节可寻址”的计算机。以字或字节为单位来表示存储器存储信息的总数,就得到了存储器的容量表示。

与速度相关的参数有:

(1)存取时间。又叫存储器的访问时间(Memory Access Time),它是指启动一次存储器

操作到完成该操作所需的全部时间。存取时间分读出时间和写入时间两种。读出时间是从存储器接收到有效地址开始,到产生有效输出所需的全部时间。写入时间是从存储器接收到有效地址开始,到数据写入被选中单元为止所需的全部时间。

(2)存储周期。存储周期(Memory Cycle Time)是指存储器进行连续两次独立的存储器

操作所需的最小间隔时间。通常存储周期大于存取时间,它包括一次存取时间加上下一次存取

开始之前的短暂附加时间,附加时间主要用于信号线上瞬变的消失或被破坏的数据的恢复。

(3)传输率。也叫存储器的带宽,指的是数据读出或写入存储器的速度,表示每秒从存

储器进出信息的最大数量,单位可用字节/秒或位/秒来表示。如存储周期为 100ns,每个存储周期可访问 32 位数据,则它的传输率为 320Mb/s。

易失性

易失性是指当断电中断后,计算机存储器存储的数据便会消失,通电以后这些数据需要重新加载。例如用半导体材料制作的 RAM 存储器,断电后里面保存的信息就消失了,这种存储器称为易失性存储器。在计算机运行过程中,考虑到RAM 存储器的易失性,一般会将RAM中的数据进行备份,即将这些数据每隔一段时间存储到非易失性存储器。如果存储器断电后仍能保存其内部信息,则称其为非易失性存储器。如磁性材料作成的存储器和只读存储器 ROM,就属于非易失性存储器。两者的最大区别是RAM在断电以后保存在上面的数据会自动消失。

随机存取存储器(Random Access Memory,RAM),也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外,见下文),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储媒介。

局部性原理早在 1968 年,Denning.P 就曾指出:程序在执行时将呈现出局部性规律,即在一较短的时间内,程序的执行仅局限于某个部分;相应地,它所访问的存储空间也局限于某个区域。他提出了下述几个论点:

程序执行时,除了少部分的转移和过程调用指令外,在大多数情况下仍是顺序执行的。该论点也在后来的许多学者对高级程序设计语言(如 FORTRAN 语言、PASCAL 语言)及 C 语言规律的研究中被证实。

过程调用将会使程序的执行轨迹由一部分区域转至另一部分区域,但经研究看出,过程调用的深度在大多数情况下都不超过 5。这就是说,程序将会在一段时间内都局限在这些过程的范围内运行。

程序中存在许多循环结构,这些虽然只由少数指令构成,但是它们将多次执行。程序中还包括许多对数据结构的处理,如对数组进行操作,它们往往都局限于很小的范围内。

局限性还表现为下述两个方面:时间局限性。如果程序中的某条指令一旦执行,则不久以后该指令可能再次执行;如果某数据被访问过,则不久以后该数据可能再次被访问。产生时间局限性的典型原因是由于在程序中存在着大量的循环操作。

空间局限性。一旦程序访问了某个存储单元,在不久之后,其附近的存储单元也将被访问,即程序在一段时间内所访问的地址,可能集中在一定的范围之内,其典型情况便是程序的顺序执行。存储器中,如磁带上,这样做还能降低存储价格2。

本词条内容贡献者为:

吴晨涛 - 副研究员 - 上海交通大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国