为了有效地抑制短沟道效应,并保持良好的亚阈值斜率,栅氧化层厚度要和沟道长度以同样的比例下降。对于0.1μm尺度的CMOS器件,栅氧化层厚度需达到3nm左右。对于超薄氧化层而言,最大的问题是会发生量子隧道穿通效应。栅氧化层的隧穿电流将随氧化层厚度的减少量指数增长,栅偏压1.5V时,氧化层厚度若从3.6nm降到1.5nm,栅电流密度大约会增长10个数量级。

氧化层的缺陷氧化层主要有三个方面的问题:

(3)硅氧化层在靠近硅的附近有很多缺陷,如高密度的电子和空穴陷阱。这些陷阱能引入快界面态,造成偏压与温度应力下的电荷不稳定性。

(2)硅与二氧化硅的热膨胀系数不同而产生了拉伸应力使硅附近氧化层产生较多的缺陷。

(3)普遍认为在硅附近100nm厚的氧化层区是属于缺陷较多的区,如氧化层局部生长速率不均匀弓I起的小斑点和氧化层针孔。1

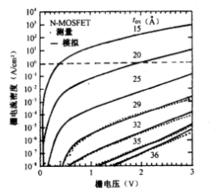

泄漏电流栅氧化层的泄漏电流通常远小于器件的导通态电流,对器件的正常工作不会产生致命的影响,但会对器件的静态功耗造成不良影响。对于下一-代纳米级CMOS器件,栅有源区的总面积可能会低于0.1cm2,此时如果电源电压V∞≈1V的话,栅电流密度的最大允许值应该在1A/cm2的数量级,由下图可知。

达到这一限制的氧化层厚度为2nm,当氧化层减薄到2nm以下,由隧穿电流引起的CMOS电路芯片的静态功耗将达到100mW数量级,这对于实际应用而言是无法接受的。换句话说,体硅CMOS沟道长度只能缩小到25~50nm,除非采用新的栅介质材料来取代现用的二氧化硅介质。动态随机存储器(DRAM)的性能对栅氧化层漏电流更为敏感,因此要求其氧化层的极限厚度更大些。

影响因素从传统的角度来看,栅氧化层的减薄会导致电场强度的增加,因而使与时间相关的击穿(TDDB)更容易发生,从而缩短器件的寿命。然而,理论和实验研究结果都证明,对于纳米级CMOS器件这个问题并不突出。

原因在于当电源电压降低到1V左右的时候,跨越氧化层的电子的能量大幅度降低,已不足以对氧化层产生损伤,因此难以发生TDDB击穿。至少在氧化的厚度2nm以上的CMOS器件中,TDDB击穿不构成限制因素。

氧化层减薄引起的另一个问题是反型层电荷的减少,器件跨导会因此而下降,这是由反型层量子化效应和多晶硅姗耗尽效应引起的。由于反型层量子化效应的存在,反型层电子密度的峰值出现在硅表面以下约1nm处,这将使等效的栅电容减小,进而使有效的反型层电荷减少。2

据估算,由此将导致等效氧化层厚度比氧化层厚度的物理厚度增加0.3~0.4nm。类似地,多晶硅栅耗尽效应也会引起等效栅电容及反型层电荷的减小。氧化层越薄,上述两种效应就越显著,对于多晶硅掺杂浓度为1020cm-3,氧化层厚度为2nm的CMOS器件,在1.5V的栅压下,反型层电荷的损失比例大约为20%。

可靠性的降低MOS晶体管的性能依赖于栅氧化层的厚度。栅氧化层厚度的降低,增强了晶体管的电流驱动能力,提高了速度和功率特性。因此在工艺缩减中降低栅氧化层厚度可以有效地提高晶体管性能,然而薄的氧化层会加重电流遂穿效应并降低氧化层可靠性。

随着现代数字CMOS工艺中栅氧化层厚度达到了几个分子层(几纳米)的水平,电源电压被栅氧层的电场所限制”。电源电压的变化会使加在栅氧层的电压高于标称电压,降低器件的长期可靠性。需要限制电源和地电压的过冲,来避免晶体管可靠性的显著下降。3

本词条内容贡献者为:

刘军 - 副研究员 - 中国科学院工程热物理研究所

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国