超前/滞后控制

超前/滞后控制是指普遍采用前置计数器和后置计数器实现触发点前后的采集样点数的控制,提出用一个计数器实现触发点前后的采集样点数的控制的方案,例如:对于存储深度深的数字示波器,可以大大减少资源,节约成本,对中价位数字示波器的生产和应用十分有利。

超前/滞后控制是数字示波器的时基电路中的核心,控制捕捉触发点前后的信息。在数字示波器的设计中,无论是实时采样示波器还是非实时采样示波器(顺序采样、随机采样)多采用了超前/滞后控制的方案。设定触发点前后的采集存储样点数,提供A/D采集转化器后的数据缓冲器以及RAM的采集使能信号和采集结束信号,用来控制向RAM中启动写和停止写采集数据,从而达到既能捕捉触发点前的信号,又能捕捉触发点后的信号。

电路核心超前/滞后控制的核心是计数器。当前,国外(如HP公司)国内的数字示波器的超前/滞后控制采用了前置计数器和后置计数器的设计方案,前置计数器用于控制存储器存储捕捉触发点前采集的采集样点数,后置计数器用于控制存储器存储捕捉触发后的采集样点数。计数器的长度决定了示波器的存储深度,前置计数器和后置计数器控制的总深度为存储深度。存储深度是示波器的性能的重要指标,存储深度越大,对感兴趣段的波形观察就越方便。

为了减少资源,节约成本,减小体积,采用CPLD(或者FPGA)设计数字示波器中的时基电路。在2Gsps实时数字采样示波器的研究项目基础上,结合研制100MHz带宽的随机取样数字存储示波器(等效采样率最大达到SGsps)的经验,我们用一个计数器设计超前/滞后控制电路,实现超前/滞后采样的控制。这对存储深度很深的数字示波器,可以大大节约计数器占用了CPLD(或者FPGA)资源。

滞后一超前校正控制系统滞后一超前校正控制系统的一种校正方式。是校正装置的传递函数的一类串联校正。

滞后一超前校正装置的传递函数中,第一项产生超前校正的作用,第二项产生滞后校正的作用。当输人为正弦信号时,此装置的输出是带有相移的正弦信号,输出信号的相移性质与输人信号的频率有关.当频率低时,相移是滞后的;当频率高时,相移是超前的。滞后一超前校正综合了滞后校正和超前校正的优点,可同时改善系统的瞬态性能和稳态性能,即兼有快速响应特性和良好稳态精度。

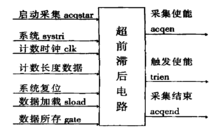

超前/滞后电路的控制信号和逻辑时序示波器的前置和后置计数器计数总深度设计为32K,前置计数器为15bit,后置计数器为15bit。两个计数器的输入控制信号有采集开始信号、系统触发信号、计数时钟、计数数据、系统复位和数据加载等信号。如图1所示。1

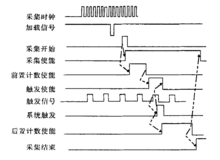

在数据所存控制信号gate有效时数据装入数据锁存器中并锁存。当采集启动信号acqstar到来时,控制逻辑电路产生数据加载信号sload,将锁存器的数据装入超前/滞后电路中前后置计数器中,并产生采集使能信号,启动前置计数器开始计数前置计数器计数满后,关闭前置计数器,产生触发使能信号,放开触发电路产生的系统触发信号systri,启动后置计数器开始工作。当后置计数器计数满数据时,产生采集结束信号,关闭采集使能信号。如图2。

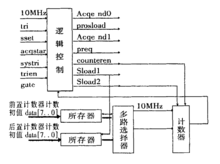

超前/滞后计数功能设计和工作原理根据前面所述的功能和时序,知道超前/滞后电路中前置计数器和后置计数器不是同时工作的,而是当前置计数器计数时,后置计数器不工作;当后置计数器计数时,前置计数器不工作,因此理论上就可以用一个计数器实现触发点前后采样点的计数。我们模拟图2中的超前/滞后电路信号时序示意图进行设计其相应的控制逻辑电路,见图3所示。为了更好地理解电路的工作原理,下面结合信号具体进行阐述。

锁存器电路中用两个锁存器(LATCH1, LATCH2)锁存经CP U解读来自示波器按键的控制信号后的数据,为计数器加载提供各种控制信号和数据。两个锁存器分别设计为16位,其中LATCH 1锁存触发点前的样点数,并给前置计数器设定初始值,LATCH2锁存触发点后的样点数,并给后置计数器设定初始值。锁存器的数据所存控制信号gate控制锁存,并为计数器置位。

计数器用一个计数器实现触发点前后的采集样点数的计数,既用于设置采集触发前的样点数,又用于设置触发信号到来后的采集样点数。计数器的设计是本电路设计的重点和难点,我们将计数器设计为同步计数器,并带有同步加载、异步置位、计数使能端,且均为高电平有效。由于其长度直接影响采集深度,我们根据厂方要求设计为32k。计数器的工作具体包括以下两个环节:

A:当系统复位后,第一次接到启动采集信号acqstar后,首先产生前置计数器加载信号,将LATCHI的初值装入计数器,并且第一次启动计数器工作。当计数器计满后输出前置计数器计数结束信号preq,且preq电平为“1",放开系统触发信号systn。

B:当系统触发信号到来时,产生后置计数器加载信号prosload信号,进而产生sload2信号,将LATCH2的锁存值装入计数器,并第二次启动计数器工作。当计数器计满后,电路中的2位计数器输出acqend0和采集结束信号(acqendl), acqendl从0变为“1”时,表示触发点后的采样点已经采满,关闭计数器的计数使能信号,停止计数器计数。

A环节和B环节的采集为一个完整的采集周期,A环节由采集启动信号acqstar启动;B环节在A环节结束后自动启动。从仿真时序图4可以看出:sloadl为A环节的同步加载信号,prosload为B环节的同步加载信号。当B环节完成后,电路进入等待状态,等待采集启动信号acqstart到来。当采集启动信号acqstar到来后,电路又进入A环节工作状态。这样周而复始地循环。当 sloadl , sload2都为"1”时,计数器处于A环节,当sloadl为“0" , sload2为“1”时,计数器处于B环节。

以上两个环节分别完成了设定的触发点前和触发点后的采集样点数,A环节完成设定的触发点前的采集样点数;B环节完成设定的触发点后的采集样点数。

电路设计保证了计数器一旦启动,且在计数期间(在完成设定的触发点前和触发点后的采集样点数之内),采集启动信号acqstar与否都不能影响计数器的工作。只有当计数器工作结束后(处于B环节),也就是当计数器完成了触发点后的设定采集样点数后,才能响应采集启动信号acqstar这样保证每次都能完成设置的采集存储深度。我们可以从仿真时序图中观察设计的结果。

电路设计的另一个信号是计数器计数使能信号preen,这是一个难点和重点。

发展和改进超前滞后控制策略中的实际微分环节、二阶超前校正环节在实际的工程实践中大量采用。然而,超前校正在改善系统动态性能的同时,其高通滤波特性也放大了高频干扰!2],往往使超前校正难以发挥其预期效果,特别在有外部高频干扰时容易造成调节机构的大幅波动,严重影响了调节机构与控制系统的品质要求,在实际工程实例中采用超前校正要非常小心谨慎。

为了克服超前策略存在的问题,在二阶超前环节的基础上,广东电网公司电力科学研究院与珠海金湾电厂提出了一种改进型超前滞后控制策略,经过工程应用的实践,证实了新型控制策略相对于常规的超前控制策略具有更好的优越性。

改良的二阶超前校正环节超前校正策略抵抗高频干扰能力较差,根源在于该环节的高频增益较大,对此,主要的改良方案为:在不改变相频特性的前提下,对幅频特性进行改造,降低高频增益,使幅频特性曲线在较宽的范围内比较平滑。这样,在较大幅度地改善系统动态性能指标的同时,又几乎不增加调节器的高频增益,在外部高频干扰时不会造成调节机构的大幅波动,使系统具有较高的稳定性和可靠性。

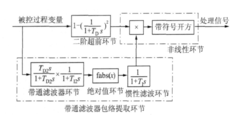

二阶超前校正环节改进实例二阶超前校正环节改进结构如图1所示。

图1中,校正回路主要由3个部分组成:二阶超前校正环节;带通滤波器包络提取环节,该环节主要作用类似于包络检波电路;上述两个环节输出信号相乘然后开方构成的非线性环节,该环节起到信号重构并保证稳态时信号增益不变之作用。在两个匹配网络中,对应的电路参数必须与整个控制回路调制出的频率相适应。

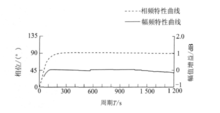

改进后二阶超前环节频率特性试验其频率特性试验结果如图2所示。

由图2可以看出,在较宽的频率范围内,改进后环节的相位几乎均为90°,而且其幅值增益近似为0dB。2

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国