概述

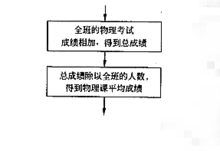

系统级以下是算法级。在这一层次上,行为描述的是系统的 数据结构和算法。算法定义了为响应给定的输入序列并产生所需的结果,该系统(主要是信息处理单元)应执行的运算和各种操作的顺序和步骤,以及本系统内部如何与外部世界进行数据交换。算法可用公式或算法流图形式来予以描述。例如,为了统计一个班同学的物理课考试的平均成绩,可以分两个“运算步”进行计算(如右图所示)。

数据结构和算法。算法定义了为响应给定的输入序列并产生所需的结果,该系统(主要是信息处理单元)应执行的运算和各种操作的顺序和步骤,以及本系统内部如何与外部世界进行数据交换。算法可用公式或算法流图形式来予以描述。例如,为了统计一个班同学的物理课考试的平均成绩,可以分两个“运算步”进行计算(如右图所示)。

第一步是将全班同学的物理考试成绩相加,得到全班同学的物理总成绩;第二步是用全班的人数去除全班的物理总成绩,得到全班物理考试的平均成绩。

同一个算法可以用软件程序完成,也可用硬件实现,采用硬件实现的最大优点是工作速度快。针对硬件实现的算法设计是一项具有挑战性和创造性的工作,这要求设计者不仅有深厚的数学知识,还要有丰富的硬件实践经验。设计算法时,必须要考虑硬件实现的可行性、设备的成本、工作速度等多种因素。

算法级在结构上描述了子系统是由哪些模块组成的。例如,在右图中,信息必理单元由数据处理器(简称处理器(processor))和控制器(controller)两个模块组成,模块之间通过数据通道和控制通道相互连接。数据处理器模块对数据进行传输、算术运算、逻辑运算等各种加工和处理工作;控制器模块向数据处理器以及其他子系统发出控制信息,使整个系统按正确的顺序有步骤地协调工作。算法级又称子系统级,它规定了组成子系统的模块的功能,但不涉及模块的内部结构。1

算法级建模方法算法级建模抽象级别很高,往往不考虑硬件实现的具体细节,一般对特大型设计或有较复杂的算法时使用。建模时往往利用高级语言,如C语言及其他一些系统分析工具(如MATLAB),对设计从算法方面进行描述。一般来说,算法级设计只用于仿真,验证系统功能,通常不支持综合,在仿真通过后,再用RTL级进行设计。因此对于复杂的系统芯片设计项目,最传统的办法是在系统级采用VHDL,在软件级采用C语言,在实现级采用Verilog。

Verilog HDL和VHDL都是用于数字电子系统设计的硬件描述语言,但两种语言的标准不统一,适应的范围也各有侧重,Verilog适合算法级、RTL级、门级,而VHDL适合特大型的系统级设计,在系统级抽象方面的功能比Verilog强大。由于两种硬件描述语言的标准不统一,导致软、硬件设计工程师之间工作交流出现障碍,工作效率较低。虽然目前VHDL和Verilog的互操作性已经逐步走向标准化,但软件与硬件的协调设计还是一个很具挑战性的工作。另外,在设计细化阶段,原始的C/C++描述必须手工转换为VHDL或Verilog HDL。在这个转换过程中会花费大量的时问,难免会产生一些错误,而且当使用C语言描述的模块转换成HDL描述的模块之后,设计人员花费大量时间建立起来的C模型将再没有什么用处。

设计者迫切需要一种语言,要求能单一地完成全部设计,支持系统级调试和系统性能分析,支持从系统级到门级的无缝过渡,能够用于描述各种不同的抽象级别(如系统级、寄存器传输级等);支持软硬件混合建模,能够胜任软硬件的协同设计和验证。System C就是目前这方面研究的最新、最好的成果,它扩展传统的软件语言C和c++,并使它们支持硬件描述,可以很好地实现软硬件的协同设计,是系统级芯片设计语言的发展趋势。2

算法级抗攻击措施目前,算法级防范DPA攻击的方法有几类,其防御思想都是相同的,主要是消除或减少算法操作数特征;消除算法执行过程中的操作数和中间值与功耗之间的对应关系。算法级防范DPA攻击的方法大致可以分为以下几类:减小信号强度、增加随机噪声、数据随机化掩盖等。

减小信号强度减小信号强度的主要实现方法包括算法执行连续编码、选取小能耗运算指令、均衡汉明重量等。算法执行连续编码可以防止DPA判断不同算法的起始点和结束点,不提供有价值的算法信息。选取小能耗运算的实现思想是用不易产生显著能耗变化的指令取代一些原始指令,使得指令的能耗减小,使得不同指令的能耗趋于平衡。均衡汉明重量可使数据以原码和反码两种形式表示,避免通过汉明重量与能耗的直接关系泄漏能量信息。

增加随机噪声增加随机噪声的方法是通过引入随机噪声使得有用的信号完全湮没于无用的噪声中,可以增加能量攻击的难度。但是,这种方法不能从根本上解决问题,其因一是攻击者可以通过有效的滤波消除干扰噪声;二是DPA本身在做统计平均时就削弱了噪声的影响。

数据随机化掩盖数据随机化掩盖可分为明文随机化掩盖和指数随机化掩盖两类。例如,分别通过数学运算的变换与反变换,使RSA算法中的操作数均为经过一定随机化变形的替代数。仅通过能量差分运算得不到真实的差异点位置,这就为真实算法做了掩盖,达到防御DPA攻击的目的。例如,RSA抗DPA的MIST算法就是一种可以防御DPA攻击的密码算法。

MIST算法是在每次RSA模幂运算时都生成一个随机的加法链来表示指数,从而随机化内部的运算;另一个特点是需要用模约减算法来生成所需的随机加法链。3

算法级的低功耗设计算法级的低功耗设计是指在确定电路实现方案时就考虑功耗问题,是从电路的体系结构和编码等方面进行低功耗设计。在电路的体系结构方面下面主要讨论并行结构和流水线技术。

并行结构降低电路的工作电压可以有效降低功耗,但同时会增加电路的延时,因此电路的设计人员在降低电路工作电压的同时,必须采取措施提高电路的工作速度,才能真正达到降低功耗的目的。并行结构是将一条数据通路的工作分解到两条通路上完成,这样每条数据通路的工作频率都为原来的一半,数据通路允许的延时增加了一倍,并且电路还可以采用较低的工作电压。这种电路结构的并行化实质上是在保持电路吞吐量的基础上通过增加电路的面积来达到降低功耗的目的。

流水线技术在电路设计时采用流水线技术,就是采用插入寄存器的办法来降低组合路径的长度,达到提高电路速度的目的。具体做法是把规模较大,层次较多的逻辑电路分为几个级,在每个级插入寄存器组暂存中间数据。

在流水线设计时,一般需要多个时钟周期来获取第一个计算结果,需要一个时钟周期来获取每级随后的计算结果。因此,采用流水线技术后系统可以在较低的时钟频率下工作,从而降低了功耗。

流水线技术的不足之处是设计的复杂度比并行结构高,需要插入寄存器,增大面积而且需要额外的时钟驱动,由此增加了时钟负载电容,导致额外的功耗开销。另外,并非所有算法均能有效地采用流水线技术,一些算法在流水线技术中可能会出现如下的情形。在理想的流水线操作中要求相邻的两条指令必须是独立的,但在实际中,若下一条指令要用到上一条指令的值,由于流水线的原因不能及时更新数据,导致下一条指令取操作数错误,从而造成流水线操作的失败。

总线编码在一个电路中或系统芯片中一般都有一条或多条总线,总线的一个基本特点是走线较长、负载较大,因此总线通常都具有较大的电容,并且这个电容的值几乎不可能改变,降低总线上的翻转频率是节省总线功耗的唯一办法。在完成同样功能的前提下要降低总线上的有效翻转频率只有改变总线上传输数据的编码。

因此,通过编码可以减少总线的动态翻转次数,并达到降低总线功耗的目的。数据总线的数据随机性较大,地址总线的地址向量连续性较大。数据总线和地址总线这两种总线传送的数值各有特点,所以针对不同类型总线的编码的算法也不一样。4

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国