当今电子系统正向高速化和小型化方向飞速发展。如何在缩小电子系统体积的同时,提高系统的速度成为摆在设计者面前的一个重要课题。随着现代科学技术的发展和计算机技术的普及,运用高速数据处理的场合越来越多。例如,高速数字信号处理系统、高速图象信息转换、语音实时处理系统等。

处理器信号处理系统中负责数据处理的核心器件就是处理器。从Intel公司发明第一款真正的通用CPU以来,各种各样的数据处理器应运而生,主要的处理器类型有:

CPU,如Intel公司的Pentium处理器,Motorola公司的Power PC,IBM公司的Cell等;

单片机,如嵌入式领域广泛应用的51系列,PIC系列,以及ARM系列等;

通用DSP,分为定点DSP,如TMS320C6000,ADSP218X等;

浮点DSP,如TMS320C67XX等;并行浮点DSP,如ADI公司的Tiger SHARC系列等;

FPGA,CPLD,主要厂商有Xilinx,Altera等;

ASIC;

专用DSP,如专用的FFT,FIR计算芯片等。

上述处理器中,CPU一般用于计算机,嵌入式设备中,作为核心处理器,负责控制及运算;单片机具有高可靠性,低成本的优势,主要用于控制领域;通用DSP则在通信,语音,图像等领域具有很广的应用;FPGA和CPLD应用非常广泛,从开始的控制领域,到现在逐渐渗透到DSP的高端运算领域,甚至在某些应用中逐渐取代DSP;ASIC则主要应用于各种量产产品中;专用DSP具有低成本的优势,主要用于语音编解码等对成本敏感的专用运算领域。

系统设计系统数字前端设计数字前端的设计主要包括ADC芯片选择,时钟设计,ADC的前端设计等。

系统存储模块设计对于存储介质的选择,采用Flash Memory,考虑到大容量使用,采用NAND型。 目前市场上量产的Flash单片容量可以达到8GB,系统要求存储容量不小于70GB,如果采用此种芯片,可以轻松满足容量要求。至于读写时间,市场上的Flash差别并不大。实际设计中采用Samsung公司的NAND型Flash芯片K9WAG08U1A。

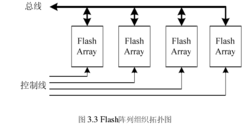

存储方案设计考虑到Flash的IO速度可以达到40MHz,我们可以想办法充分利用该特性,增加读写带宽,在此我们利用了乒乓工作思想。将Flash分为四组并联,首先,对第一组进行IO操作,在该组编程的时间里,去对第二组进行IO操作,如此往复,这样就充分利用了Flash的写等待时间,利用了IO的带宽,四组并联理论上就可以达到40MHz的IO工作频率。组织拓扑结构如图所示,四组Flash共享数据地址总线,控制线分开,分时操作,分时占用总线,这样就可以充分利用总线带宽。

本系统具有多通道,高速的数据采集前端,要求作为控制器的FPGA必须具有足够的IO带宽及数目,同时为了满足后端海量数据的实时处理,对其DSP处理能力及内存大小也有很高的要求,因此,我们必须考虑使用高端的FPGA产品。

在选取DSP时,要考虑DSP的运算能力,还要考虑其内部存储空间大小、外部存储空间的扩展能力、与外部的数据通讯能力以及系统设计的复杂度、编程难度等。在实时雷达成像信号处理系统中,运算量大、数据吞吐量大的特点,同样要求我们必须选用高端的DSP产品。目前,能提供高端通用DSP产品的公司只有ADI和TI公司。

混合信号电路的设计很复杂,元器件的布局、布线以及电源和地线的处理将直接影响到电路性能和电磁兼容性能。模拟信号和数字信号的转变是否实时、精确,是电路设计的重要指标。除了器件工艺、算法的进步会影响系统数模变换的精度外,现实世界中众多干扰、噪声也是困扰数模电路性能的主要因素。数模混合设计中的干扰问题,可从干扰源、干扰途径和受害者三个方面分析,也就是电磁兼容分析中的三个基本要素。模拟信号是随时间变化连续变化的电压或电流,它们对外部的干扰更敏感,因而通常作为受害者做分析;数字信号上只有随时间变化的门限量化后的电压成分,相比模拟信号对干扰有较高的承受能力,但是这类信号变化快,特别是快速变化的边沿具有较高的高频谐波成分,对外辐射能量,通常作为干扰源;干扰途径主要包括电路传导耦合和空间电磁场耦合。这样,降低数字信号对模拟信号的干扰就可以通过抑制干扰源、保护受害者、切断干扰途径三种方法来实现。

ADC 前端输入配置方式选择目前的设计中,ADC前端输入配置方式主要可分为两种方式,一种是有源器件,另外一种是用无源器件。其中,有源器件通常使用放大器,无源器件主要用变压器,两者各有特点。我们可以根据两者各自的特点,选择合适的前端输入配置方案。一般来说,在高中频采样时,要求大带宽,低噪声,或者对功耗有要求的场合,选用变压器;而增益要求高,通带平坦度要求高,以及需要保留直流分量的场合要用放大器输入方式。当有多个参数发生冲突时,要分清主次,权衡选择。

ADC采样时钟设计在A/D转换过程中引入的噪声来源较多,主要包括热噪声、电源纹波、参考电平纹波、采样时钟抖动、ADC固有孔径抖动以及量化误差引起的噪声等。量化错误引入的噪声不可避免,但我们可以采取措施以减小引入ADC的其他噪声。前面已经讨论了电源、地的设计,以及ADC前端的设计,除此之外,采样时钟抖动对ADC信噪比性能也有着关键影响。

信号完整性分析常遇到的信号完整性的问题有振铃,反射,近端串扰,地弹,衰减,时延,过冲等等,这些问题可能造成数字逻辑时序错误,噪声导致电平判断错误,以及EMI等问题。实际上,所有的信号完整性问题,可以归结为下面四类:单一网络的信号完整性问题;两个或者多个网络间的信号完整性问题;电源和地分配系统中的轨道塌陷;电磁干扰问题。1

新技术展望强大的处理能力是信号处理器不断追求的目标,大容量、高速度是存储领域不变的主题,速度、精度则是模数转换器厂商努力的方向。

处理器处理能力主要通过提高主频,革新架构,并行处理等方法来提高,其中,提高主频在当前半导体工艺下,很容易遭遇瓶颈,革新架构则需要长时间的积累发展,并行处理则是当前业界最为热衷的提高处理器处理能力的方法,并行处理也是当前数据处理领域的发展方向。

图形处理器在通用计算领域的应用二十世纪八十年代,出现了以GE(Geometry Engine)为标志的图形处理器,一直以来,GPU都作为专用图像处理器完成各种图形数据处理工作。GPU的发展非常迅猛,几乎以每半年性能就会提升一倍,随着GPU性能的不断提升,开始有人提出了GPGPU的概念,即将GPU用于图形处理以外的通用计算领域。2003年,世界上唯一的图形学硬件年会(SIGGRAPH/EUROGRAPHICS Graphics Hardware 2003)将其重点转向了计算机图形处理器的非图形应用,甚至有人提出了General Processing Unit的概念。

固态非易失性存储技术新进展容量和速度的提高是存储的不断追求的目标,当前在固态存储技术里面,Flash是市场主流,各大厂商一方面不断完善Flash技术,另一方面,也在不断的探索Flash的替代技术。

Flash技术不断发展,但是写入速度慢、擦写次数少等固有缺陷催生了其他代替技术的出现。几年来,通用存储(universal memory)的概念不断被提及,即利用单一存储器架构实现易失性存储器具有的高速特性和非易失性存储器具有的大容量特性。在各类技术中,磁性随机存取存储器 (Magnetic RAM,MRAM)、铁电存储器(Ferro electric RAM,Fe RAM)及相变存储器(Phase Change Memory,PCM)三种最为突出。

高速模数转换器技术新进展数模转换器(ADC)按照技术类型可以分为三种,半导体ADC,超导材料ADC和光学ADC。半导体ADC是目前应用最为广泛的ADC,前面讨论的ADC分类都属于半导体ADC,目前半导体ADC的采样精度可达24-bit,采用锗化硅工艺的ADC速度最高可达12.5 GSPS,但是由于半导体材料的特性限制,很难再提高其采样率。半导体ADC是目前应用最为广泛的ADC,前面讨论的ADC分类都属于半导体ADC,目前半导体ADC的采样精度可达24-bit,采用锗化硅工艺的ADC速度最高可达12.5 GSPS,但是由于半导体材料的特性限制,很难再提高其采样率。 超导材料ADC的速度比常规材料的速度要高出一个数量级,但是它必须在低温下才能表现出超导特性,限制了它的应用。 光学模数转换技术最初由S.Wright等人于1974年提出,之后不断有新的技术方案产生。随着光通信技术的发展,光学ADC技术也得以不断进步,从90年代初开始的,通过借鉴光通信中的技术,提出了时分复用和波分复用的技术方案。理论上,光学ADC可以做到上千GHz的采样率,如果这得以实现的话,雷达接收机就可以直接在射频采样,不需要经过混频,可以极大的改善接收机性能。目前,采用光学模数转换技术的一种器件做到了18 GSPS的采样速率和7-bit的采样精度。美国国防高级研究计划局也计划投入约4000万美元开发1000 GSPS采样速率的模数转换装置。 目前,光学ADC还处于开发阶段,系统还非常复杂,要真正实现实用,尚需要材料等技术上的突破。1

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国