数据采集单元又称模拟量输入系统,它的作用是隔离、规范输入电压,并将模拟输入量转换成微机系统所需的数字量,以便与CPU接口。模拟量输入系统是微机保护装置中很重要的电路,保护装置的动作速度和测量精确度等性能都与该电路密切相关。1

数字强震动记录器的数据采集单元主要由模数转换器(ADC)和数字信号处理芯片(DSP)组成。模数转换器是一种过采样模数转换器,它把由传感器输入的模拟信号(电压)经放大后转换成高采样率的数字数据流,再由24位数字信号处理芯片对其进行去假滤波,输出所需采样率的数字数据流。

去假频滤波是模数转换中必须具备的一步。根据采样定理,对模拟信号以一定采样率采样后,大于1/2采样率的频率成分将成为假信号混叠到有效信号带宽内,造成数字化信号的误差。因此必须滤去这种假频信号。过采样方法就是先将模拟信号初滤波,模拟滤波器的拐角频率可取得很高,是信号最高频率 的几十倍,滤波器的带外斜率不必很大,这样就大大降低了模拟滤波器的制作难度。再以远大于

的几十倍,滤波器的带外斜率不必很大,这样就大大降低了模拟滤波器的制作难度。再以远大于 的采样率对经初滤波的信号进行数字化,得到高采样率的数字化信号。过采样的数据进入24位数字信号处理器后,用数字滤波器进行去假滤波,将大于五的频率滤去,然后经抽样得到所需采样率的数字化数据。

的采样率对经初滤波的信号进行数字化,得到高采样率的数字化信号。过采样的数据进入24位数字信号处理器后,用数字滤波器进行去假滤波,将大于五的频率滤去,然后经抽样得到所需采样率的数字化数据。

衡量数据采集单元性能的主要技术指标是分辨率、采样率、噪声和动态范围等。2

性能指标采样率数字强震动记录器至少应该具备多个不同档次的采样率供选择使用。采样率与可以从记录中获取的最高频率成分有关,强震动观测中常用的采样率为100次/秒和200次/秒,相应可以分辨的最高频率成分分别为40Hz和80Hz。显然,高采样率的记录比低采样率的记录所占的存储空间大,而且高采样率记录的数据传输时间也长。

噪声记录器的噪声大小是指在无传感器输入信号情况下记录器本身的记录采样输出值大小,通常用噪声均方根值 来表示。记录器噪声的大小直接影响到记录器的动态范围。

来表示。记录器噪声的大小直接影响到记录器的动态范围。

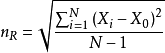

在记录器各通道输人端短接并接地情况下,记录其 个采样数据

个采样数据 ,则记录器噪声均方根值

,则记录器噪声均方根值 为

为

式中 为

为 的平均值,

的平均值, 的单位为伏

的单位为伏 。

。

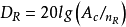

记录器的动态范围定义为满量程输入和噪声(均方根值)之比的常用对数与20的乘积,用分贝(dB)表示。

式中,

式中, 为满量程输入时采样记录的有效值,

为满量程输入时采样记录的有效值,

式中, 为满量程输入时采样记录的振幅值,单位为伏

为满量程输入时采样记录的振幅值,单位为伏 。 ’

。 ’

记录器的动态范围表示记录器能记录的最大值与最小值之间的倍数关系。数字强震动仪记录器的动态范围应不低于90dB。

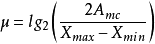

分辨率分辩率是指满量程输入时,记录器采样数据的二进制编码输出扣除其噪声影响后的有效位数。数字强震动仪记录器的分辨率 应不小于16位。

应不小于16位。

式中, 为记录器满量程输人时,与输入信号振幅对应的采样值。

为记录器满量程输人时,与输入信号振幅对应的采样值。 为记录器输入端短接时采样数据的最大值。

为记录器输入端短接时采样数据的最大值。 为记录器输入端短接时采样数据的最小值。

为记录器输入端短接时采样数据的最小值。

计算时,如果 ,则取

,则取 。

。

将记录器的输出与输入之比表示为输入信号频率的函数,称为记录器的频率响应。通常以幅频特性曲线表示幅值与频率的关系,以相频特性曲线表示相移与频率的关系。理想的幅频特性曲线应该是在需要的频率范围内为一平坦的直线,即输出输入之比不随频率而改变。理想的相频特性曲线应该是在需要的频率范围内为一斜直线,即相位呈线性变化。数字强震动仪记录器至少应在0~50Hz范围内,其幅频特性曲线是一条平直线,相频特性曲线为一斜直线(线性相移)。2

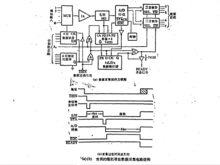

基本结构类型常规随机寻址数据采集单元 右图是目前常用的数据采集电路设计框图,MUX采用8~16个模拟多路转换器,会用一个数据放大器、S/H电路、A/D转换器,同时包括必须的时序和控制逻辑,因此能保证规定精度所要求的建立时间。这种组件系统的利用率高,经济成本合理。系统的工作原理分析如下:

右图是目前常用的数据采集电路设计框图,MUX采用8~16个模拟多路转换器,会用一个数据放大器、S/H电路、A/D转换器,同时包括必须的时序和控制逻辑,因此能保证规定精度所要求的建立时间。这种组件系统的利用率高,经济成本合理。系统的工作原理分析如下:

(1)通道的选择

模拟多路开关MUX具有16个基本通道,通道译码选择是通过6位地址比较器和4位数据锁存器完成的。6位地址译码输入可以扩展到64个通道。4位数据锁存器接入低4位地址,用来选择16个基本子通道,片选信号是由6位地址比较器译码发出的。

(2)12位转换数据的传输控制

本系统采用12位逐次比较型ADC,与微处理器8位数据总线连接,因此转换数据根据地址 的状态需进行二次传输。当

的状态需进行二次传输。当 时,送高4位数据。如果

时,送高4位数据。如果 “或”门

“或”门 输出为低,三态锁存器选通转换数据读出。

输出为低,三态锁存器选通转换数据读出。

(3)气数据采集的时序控制

由于信号的采集和转换需要一定的建立时间来保证精度要求。因此数据采集模块的工作进程是需要进行定时控制的,这由右图中的单稳74221来完成。

当MUX中的一个子通道选通后,数据总线有效状态信号 ,6位地址比较器输出端

,6位地址比较器输出端 为低,则“或”门A输出为低。使“或”门

为低,则“或”门A输出为低。使“或”门 为

为 信号的发出准备逻辑条件,“或”门B的输出,触发单稳

信号的发出准备逻辑条件,“或”门B的输出,触发单稳 的

的 端,产生

端,产生 的采样定时脉冲,于是

的采样定时脉冲,于是 组件处于跟踪工作方式。这一过程是与MUX的通道选择同时进行的,直到

组件处于跟踪工作方式。这一过程是与MUX的通道选择同时进行的,直到 启动命令发出为止。

启动命令发出为止。

在采样延时结束后,单稳 端输出为低,

端输出为低, 端被触发,经

端被触发,经 后,

后, 端输出触发

端输出触发 端,

端, 开始转换直到

开始转换直到 ,该状态信号使数据锁存器

,该状态信号使数据锁存器 的

的 端和门

端和门 输出均为低,三态输出锁存器选通。同时,向

输出均为低,三态输出锁存器选通。同时,向 发出

发出 信号表示转换经束。

信号表示转换经束。

在转换数据未被读入内存前,单稳状态不变,因此 数据一直保持有效。电路的时序波形如右图(b)所示。假设采样延时为

数据一直保持有效。电路的时序波形如右图(b)所示。假设采样延时为 ,

, 转换时间为

转换时间为 ,一次转换周期为

,一次转换周期为 。

。

这种结构的唯一缺点是 要等待

要等待 发出

发出 状态信号后,才向

状态信号后,才向 发齐备信号

发齐备信号 。所以在时间上和效率上不是非常理想的结构,但它能适用于大多数场合,是目前广泛应用的电路结构。

。所以在时间上和效率上不是非常理想的结构,但它能适用于大多数场合,是目前广泛应用的电路结构。

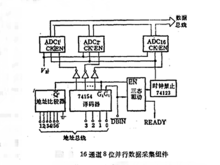

右图是一种快速16通道并行转换数据采集结构,图中电路由16个 组成,由同一个译码器进行译码选择,输出构成“或”逻辑汇集于数据总线。它的最大优点是能够直接存

组成,由同一个译码器进行译码选择,输出构成“或”逻辑汇集于数据总线。它的最大优点是能够直接存 取数据,电路设计简单。但必须考虑性价比。右图上省略了

取数据,电路设计简单。但必须考虑性价比。右图上省略了 组件和数据锁存器,而这些对一个快速系统显然是需要的,因此众多元件的价格限制了它的广泛应用。随着单片集成

组件和数据锁存器,而这些对一个快速系统显然是需要的,因此众多元件的价格限制了它的广泛应用。随着单片集成 价格的下降,它将是比较理想的高速结构。

价格的下降,它将是比较理想的高速结构。

右图中采用一个4~16线的地址译码器对16个 进行选通。如果转换时间在存贮器读写期之内,则不需要插入机器的等待周期,这时

进行选通。如果转换时间在存贮器读写期之内,则不需要插入机器的等待周期,这时 像操作存贮器一样读取数据。译码器

像操作存贮器一样读取数据。译码器 的控制,是由6位地址比较器的

的控制,是由6位地址比较器的 端信号以及

端信号以及 数据有效信号

数据有效信号 完成的。三态驱动器用来控制时钟信号和

完成的。三态驱动器用来控制时钟信号和 信号。当

信号。当 是读出状态时时钟被禁止,这时

是读出状态时时钟被禁止,这时 不工作以保证

不工作以保证 数据的有效性。

数据的有效性。

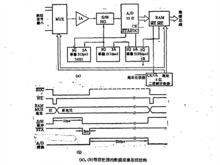

与上述两种类型相比,配有存贮器(RAM)的多通道数据采集组件的性价比最好,效率最高。由于配备了专用的RAM,所以 可直接读取RAM中数据,不需要等待外围设备的齐备信号。也不必编写专用的

可直接读取RAM中数据,不需要等待外围设备的齐备信号。也不必编写专用的 子程序,只要读出

子程序,只要读出 或

或 状态标志就足够了。

状态标志就足够了。

右图原理框图中采用4 x 6的RAM,软换后的有效数据直 接存放在RAM中。电路采用二进制计数器进行MUX通道选择和RAM数据的更新;三个单稳电路用来完成转换的时序控制。

接存放在RAM中。电路采用二进制计数器进行MUX通道选择和RAM数据的更新;三个单稳电路用来完成转换的时序控制。

通道译码选择和前面两种类型略有不同。因为每一采样通道转换的数据是和RAM单元中存放的数据一一对应的。所以在进行下一次新的采样时,MUX通道的变更和:RAM地址更新同步进行。计数器的4位地址输出,同时对MUX和RAM进行寻址。而计数器时钟OK端则由译码的地址比较器输出控制。

时序控制是由单稳电路组成,其基本原理与右图类似,我们通过右图(b)的时间波形来讨论这一过程。

当转换结束时,转换结束状态信号 ,单稳

,单稳 端被触发,

端被触发, 向RAM的

向RAM的 端发一个写入脉冲。

端发一个写入脉冲。 转换数据存入RAM中。同时清除二进制计数器,送出通道和RAM的新地址,准备下一次数据转换。

转换数据存入RAM中。同时清除二进制计数器,送出通道和RAM的新地址,准备下一次数据转换。

此外单稳1的 端同时触发单稳2的

端同时触发单稳2的 端,起动采样/保持电路,触发脉宽取决于采样信号的建立时间,本电路取为

端,起动采样/保持电路,触发脉宽取决于采样信号的建立时间,本电路取为 。经

。经 延时后,单稳2的

延时后,单稳2的 输出端信号使

输出端信号使 在保持方式工作,由单稳3发出一个

在保持方式工作,由单稳3发出一个 启动信号至

启动信号至 端,经

端,经 后完成数据转换并存入RAM。在模拟读出状态时,单稳1的

后完成数据转换并存入RAM。在模拟读出状态时,单稳1的 端由原来的0变为1使单稳锁住,以保证可靠的读数。

端由原来的0变为1使单稳锁住,以保证可靠的读数。

这种电路可以使 能够任意地选择RAM地址和读出MUX中的相应通道数据。这是由于地址比较器的输出,RAM地址输入和二进制计数器的输出都连接到地址总线上。3

能够任意地选择RAM地址和读出MUX中的相应通道数据。这是由于地址比较器的输出,RAM地址输入和二进制计数器的输出都连接到地址总线上。3

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国