近来,微电子器件及其逻辑电路的可靠性和抗辐射性能受到了研究者广泛的关注 ,这个特征对于新兴的纳米级磁性逻辑器件也不例。

磁性逻辑器件(Magnetic Logic Device ,MLD) ,也可称作磁性量子元胞自动机(Magnetic Quantum Cellular Auotmata ,MQCA),是一种利用纳磁体间偶极子场作用进行信息处理和传递的新兴纳电子器件,由Cowburn等首次提出。和传统CMOS 以及其它新兴器件相比,MLD 除了具有极低功耗优点外,其最重要的优势是具有天然非易失性和抗辐射功能,这些特征使其在空天电子领域具有广泛的应用前景。

虽然磁性逻辑器件相比CMOS 而言在实现相同的功能(例如择多逻辑门)下占用更少的版图面积,但是随着片上集成密度的增加,纳磁体尺寸会越来越小,而此时能否获得可靠的电路转换极为重要。

磁性逻辑器件结构MLD通常由长方体纳磁体构成,这是因为拉长的长方形纳磁体具有明显的形状各向异性,易于实现双稳态(‘0’和‘1’)。然而,研究表明当MLD 电路中含有多于五个纳磁体或一个以上的择多逻辑门时,磁性逻辑器件极易受杂散磁场的影响而发生自发和无序翻转。这些杂散磁场或来源于非对称的纳磁体版图结构,或来源于温度波动引起的微小热耦合场。目前常用的增加磁性逻辑器件稳定性的方法是采用二轴各向异性和多重磁晶各向异性纳磁体以及慢变旋转磁场时钟。改变各向异性是一种很有效的解决方法,但其需要外延生长工艺进行纳磁体制备,不利于实现多层磁逻辑结构;而慢变旋转磁场时钟则大大降低了电路的工作速度。因而磁性逻辑的可靠转换迫切需要设计出简洁和稳定的器件结构。

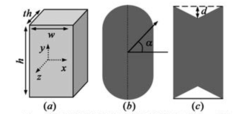

图1( a)所示为纳米磁性逻辑器件,它采用拉长形状的单畴纳磁体构成(单畴是指纳磁体内所有磁化是大致相同的,可等效为一个巨大的经典旋转),纳磁体的大小可表示为宽× 高× 厚(w × h × th)。x-y平面上,MLD 的长轴通常被视为易磁化轴,即图1( a)中的y方向;短轴则为难磁化轴,即图1( a)中的x 方向;z 轴表示厚度。通常情况下可采用如下逻辑编码方法,如磁化方向朝上或朝下可分别用于编码逻辑‘1’或‘0’ ,而沿难磁化轴朝右或朝左的磁化则为空态‘。纳磁体之间的偶极子耦合产生了‘0’和‘1’指向交替出现的反铁磁排序(Antiferromagnetic Ordering ,AFO)和指向相同的铁磁排序(Ferromagnetic Ordering ,FO) ,这两种排序的组合可实现有用的磁性逻辑门电路。图1( b)所示为正常形状的圆角长方形纳磁体(x-y平面图) ,其中α表示瞬态磁化方向和短轴的夹角。图1( c)所示为对称缺失等腰三角形特殊形状纳磁体,其中等腰三角形的底边和纳磁体的宽度相同,d表示等腰三角形的高度。

图1

图1

MLD 的转换机制为:沿着器件难磁化轴施加一个微小的磁场将纳磁体磁化到空态(这个微小的辅助磁场就是磁性逻辑器件的时钟),随后该器件会在邻接纳磁体的偶极子场作用下翻转到期望的逻辑态1。

磁性择多逻辑电路反相器是CMOS 中的基本电路,而MLD 中的信号反相是通过反铁磁耦合实现的,图2中虚线方框描述的两个纳磁体即是一个最简单的磁性逻辑反相器。这里右向代表逻辑‘1’ ;左向代表逻辑‘0’ ;朝上或朝下为空态。磁性择多逻辑门电路如图2所示,它由十字形放置的五个纳磁体构成,三输入共有八种配置组合。

图2

图2

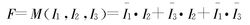

图2中, 、

、 和

和 为输入纳磁体,F为输出纳磁体;虚线箭头给出的磁化指向为其中一种稳态配置。注意磁性择多逻辑门与早期的电性量子元胞自动机择多逻辑门完全不同,这是因为磁性逻辑器件中存在两种不同机理的耦合形式。通过OOMMF软件穷尽模拟8个输入逻辑组合得出了不同情况下的纳磁体磁化指向,进而推导出其逻辑表达式(能够实现输出

为输入纳磁体,F为输出纳磁体;虚线箭头给出的磁化指向为其中一种稳态配置。注意磁性择多逻辑门与早期的电性量子元胞自动机择多逻辑门完全不同,这是因为磁性逻辑器件中存在两种不同机理的耦合形式。通过OOMMF软件穷尽模拟8个输入逻辑组合得出了不同情况下的纳磁体磁化指向,进而推导出其逻辑表达式(能够实现输出 、

、 和

和 变量组中出现次数较多的逻辑态)为:

变量组中出现次数较多的逻辑态)为:

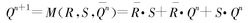

触发器是具有记忆功能、能存储数字信息的最常用的一种基本时序单元电路,但目前还未见采用磁性逻辑器件实现时序电路的报道,主要原因也在于大量纳磁体和多个逻辑门的整体传递行为非常复杂,要实现可靠转换比较困难。一个简洁的非钟控RS触发器(无CP脉冲控制信号),其电路图如图3所示。这个电路用到了两个反相器和一个择多逻辑门,其逻辑表达式为:

该触发器实现的功能是:当两输入值R和S相等时,触发器输出保持为先前的逻辑态;当R=0、S=1时,其输出为逻辑‘1’;当R=1、S=0时,其输出为逻辑‘0’。

图3

图3

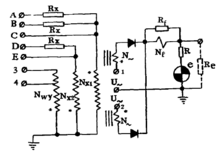

LC1型磁性逻辑元件是利用磁性放大器工作在继电状态下——磁继电器的原理来构成的。其基本线路如图4,基本特性如图5。

图4

图4

图5

图5

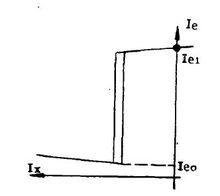

图5所示的继电特性类似有接点继电器的控制特性,有着两种稳定的工作状态—元件输出状态 (工作在特性的上限)和元件干扰状态

(工作在特性的上限)和元件干扰状态 (工作在特性的下限),相当于继电器的起动状态和释放状态。

(工作在特性的下限),相当于继电器的起动状态和释放状态。

元件的基本线路中共有两个控制器组 及

及 以及一个位移绕组,它们的极性已在图4中标出。只要适当地改变引入位移安匝的大小及部分外部连线即能得到表1所示的五种基本基辑元件和多种复合是辑元件(“和——记忆”复合,“是——否”复合等等),所以本型逻辑元件亦有万用元件之称2。

以及一个位移绕组,它们的极性已在图4中标出。只要适当地改变引入位移安匝的大小及部分外部连线即能得到表1所示的五种基本基辑元件和多种复合是辑元件(“和——记忆”复合,“是——否”复合等等),所以本型逻辑元件亦有万用元件之称2。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国