基本概念

并行系统(parallel system)是指同时执行多个任务或多条指令或同时对多个数据项进行处理的系统。早期的计算机是串行逐位处理的,称为串行计算机。随着计算机技术的发展,现代计算机均具有不同程度的并行性。

并行操作系统是一种挖掘现代高性能计算机和现代操作系统的潜力的计算机操作系统,能够最大限度地提高并行计算系统的计算能力1。

并行处理系统结构所有的并行处理系统均可视为以处理器为节点的网络。设计并行处理时必须考虑许多问题,其中的两个重要问题是处理系统的网络拓扑结构和节点处理器的设计。高速数字信号处动系蛛属于专用机,其拓扑结构和节点设计与所要实现的算法有密切的关系,且对其通用性不需要而且也不应该有很高的要求(通用机有很高的通用性,但相应地有很大的管现开销)。良好的专用并行处理系统应具有如下一些共同特点。

(1)模块化处理系统由种类不多的模块组成。这既便于节点及通讯硬软件设计,又便子系统的扩展,而且也降低了系统的复杂性;

(2)流水处理这可以大大提高处理速度,是并行系统必须具有的特点之一;

(3)局域性这包括局域的数据流和控制流。由于无论在芯片级还是系统级,通讯问题均是关键,因而局域性非常重要。

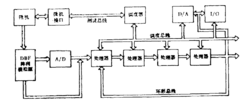

并行处理系统的框图如图:

处理系统的中心部分由一个调度器及四个处理器组成,系统设计成可以很易扩展其处理器的数量,系统还包含A/D、D/A及串口和并口。系统的重构通过对调度器和其它处理器的软件设置实现。系统可设置成线性、环形、星形、车轮形等各种结构形式,以适于多种应用。

调度器亦是一个处理器,用于系统的调度和控制,也可完成一定的处理运算。它主要用于向处理器发出各种控制命令,控制调度总线的复用,转发微机和各处理器之间的控制和数据。所有程序和初始数据均由微机产生,再经由调度器转至各处理器。要显示打印的结果亦由调度器转至微机。

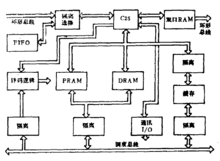

系统的运算主要由处理器完成。现系统有 个接水上一样的处理器,只是在第一个处理器中加入FIFO,用于作为输入数据通道。处理器的组成如图:

系统共有三种总线: 测试总线、调度总线和环形总线。测试总线用于传输微机和处理系统间的数据、微机向处理系统传送程序、初始化信息及控制命令;调度总线完成调度器和其余处理器的信息传输;环形总线将四个处理器连接成环形结构。

并行处理器是实时实现许多需要完成复杂计算(如矩阵计算)的数字信号处理系统的不可避免的选择2。

结构原理并行处理计算机的结构主要有流水线方式 、多功能部件方式 、阵列方式、多处理机方式和数据流方式。

流水线处理机将指令的执行过程分解为若干段,每段进行一部分处理。一条指令顺序流过所有段即执行完毕获得结果。当本条指令在本段已被处理完毕而进入下段时,下条指令即可流入本段。因此,在整个流水线上可以同时处理若干条指令。若各段的执行时间均为一个时钟节拍,则在正常情况下每拍可以输出一个结果,即完成一条指令。这就可加快处理机的速度。

程序中相邻指令的相关性会影响流水线处理机效率的发挥。例如,条件转移指令在上条指令执行完以前,有时不能确定后继指令;又如本条指令需要用上条指令的结果作为操作数等,都将中断流水线而使效率下降。

多功能部件一台处理机具有多个功能部件。各功能部件可以并行地处理数据,因而处理机可以使用不同的功能部件并行执行几条指令,以提高处理速度。如有的计算机具有浮点加、定点加、浮点乘、浮点除、逻辑操作、移位等多个对不同数据进行处理的功能部件。一些流水线向量机也含有多个功能部件。程序在执行中因对各部件的需求不平衡,各功能部件不可能全部处于忙碌状态。指令间的相关性也影响机器的效率,如本条指令所需的功能部件尚在执行其他指令;又如本条指令所需操作数恰为尚未执行完毕的指令的结果等。

阵列处理机一台处理机由多个相同的处理部件和一个统一的控制器组成。这个控制器解释指令并传送操作命令至全部处理部件。各处理部件按照控制器的命令同时进行完全相同的操作。阵列处理机又可分为浮点阵列处理机和位片式阵列处理机两类。

ILLIAC-Ⅳ机属于浮点阵列处理机,包括64个完全相同的处理部件(PU)和一个公共的控制部件(CU)。每个处理部件包括一个能执行64位浮点操作的处理单元(PE)和一个容量为2k字的存储器(PM)。64个处理部件排列成8×8阵列。每个处理部件与四邻处理部件均有直接数据通路。

多处理机系统多处理机系统能提高系统的性能和可靠性。它是多指令流多数据流处理机。根据系统中各处理机的耦合程度,多处理机系统可分为两类。①非直接耦合的多处理机系统:系统中各处理机均有主存储器。各处理机由各自的操作系统进行管理,它们通过共享的输入输出系统进行通信。②直接耦合的多处理机系统:系统中各处理机共享主存储器,并受统一的操作系统管理。多处理机系统一般指直接耦合这一类。

数据流处理机数据流处理机是受到人们重视的高度并行的处理机。它虽保留了存储程序的做法,但在主要原理上已与诺依曼计算机结构不同。它不按程序计数器指出的指令顺序执行程序,只要所需操作数全部具备,指令即可被执行,亦即程序的执行不是由控制流驱动,而是由数据流驱动。

数据流处理机是以语言为基础的处理机。它使用数据流程序图作为用户语言与计算机结构之间的接口。数据流程序图用能动框表示 。每个能动框有多个域 ,分别存放操作码、操作数和目标地址。数据流程序以能动框集合的方式保存在能动存储器中。当某条指令可以执行时,相应的能动框地址便被送入指令排队器。读取部件则按地址从存储器中取出该能动框,形成操作包,送至操作部件进行处理,产生结果包。修改部件根据结果包的目标地址将结果数据送至规定的能动框作为操作数,并将具备操作数的指令的地址送至指令排队器。指令排队器中的指令均具备执行条件,因而只需增加部件数量或增强部件流水程度 , 就可以高速并行执行。此外,还可将多个指令处理单元连接成数据流多处理机系统,进一步提高处理能力。

并行算法和并行语言提高并行处理效率的关键之一是并行算法。算法须适应计算机的结构。如果一种算法所表达出来的并行度与计算机的并行度基本一致,便能提高计算机的解题效率。

在向量计算机中,提高并行度的主要问题在于把可并行处理的操作数用向量表示。许多常用的数值计算法,如数列求和、矩阵乘、高斯消元、快速傅里叶变换等,已成功地在向量计算机上实现了并行处理。较为通行的并行语言基本上是FORTRAN语言的扩展。

在多处理机系统中,提高程序并行性的关键,是把任务分解成足够多的可同时操作的进程。在程序语言中,还须扩充能明确表达进程并发性的语句,以便程序运行时能为相应的控制机构提供控制和管理手段,其中包括并行任务的派生、通信和调度。ADA 语言为描述多处理机并行程序结构提供了必要的语句。为适应数据流计算机而出现的若干数据流语言如Id语言和VAL语言已经在试用。 其重要特点是把数组看成是值而不是目标。用数据流语言编写的程序能够自然地表达出最大的运算并行性。

并行处理器系统的种类如果按性质来进行分类,则有些处理器是模凌两可的:既可算作这一类,又可算作另一类;按照费林的意见,又可分为单指命流多数据流系统和多指令流多数据流系统。这里列出的只是一些重要的应算作并行处理器的系统3 :

(1)向量/流水线处理器:

STAR-100(CDC公司)

CYBER 203/205(CDC公司)

T1-ASC(德克萨斯仪表公司)

Cray-1(克雷研究公司)

(2)并行处理器系统

ILLIAC IV(依里诺斯大学,布劳斯公司)

SOLOMOM(西屋公司)

PEPE(贝尔实验室、布劳斯公司系统发展公司)

BSP(布劳斯公司)

DAP(ICL公司)

CHOPP(哥伦比亚大学;苏里万学会)

C.mmp.Cm(卡内其/梅隆大学)

T16(Tandem公司)

EGPA(埃尔朗根/诺尔贝尔格大学)

(3)相联处理器

STARAN(古得依尔宇航公司)

ECAM(霍尼威尔公司)

OMEN(商特尔公司)

ALAP(休斯飞机公司)

(4)算法数组处理器(流水线计算机)

IBM 2938/3835(IBM公司)

MAP III(数据控制公司)

UAP(尤尼瓦克公司)

AP-120B/190L(浮点系统公司)

FPS-164(浮点系统公司)

ATP(Datawest公司)

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国