基本概念

Masupka等人利用只有1只晶体管的 单元和新的擦除编程电路技术及高速灵敏度放大器,于1987年报道了第一块256kb闪速

单元和新的擦除编程电路技术及高速灵敏度放大器,于1987年报道了第一块256kb闪速 (即闪速存储器)。之所以称为闪速,是因为它能同时、快速地擦除所有单元。闪速存储单元是取代传统的EPROM和

(即闪速存储器)。之所以称为闪速,是因为它能同时、快速地擦除所有单元。闪速存储单元是取代传统的EPROM和 的主要非挥发性(永久性)的存储单元。

的主要非挥发性(永久性)的存储单元。

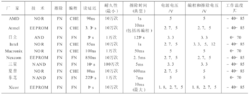

闪速存储单元的工作原理单元的工作原理主要有两种技术来改变存储在闪速存储器单元的数据:沟道热电子注入(CHE)和Fowler-Nordheim隧道效应(FN隧道效应)。所有的闪速存储器都采用FN隧道效应来进行擦除。至于编程,有的采用CHE方法,有的采用FN隧道效应方法。下表给出了几家主要闪速存储器厂家的存储单元性能。

表1

表1

由于在CHE注入过程中,浮栅下面的氧化层面积较小,所以对浮栅下面的氧化层损害较小,因此其可靠性较高,但缺点是编程效率低,FN法用低电流进行编程,因而能进行高效而低功耗的工作,所以在芯片上电荷泵的面积就可以做得很小。

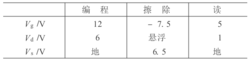

为了减少闪速存储器的单元面积,可以采用负栅压偏置。由于在字线(接存储单元的栅)上接了负压,接到源上的电压就可以减小,从而减少了双重扩散的必要性所以源结可以减小到0.2μm。负栅偏置的闪速存储器还有一个优点,就是通过字线施加负压可以实现字组(sector)擦除(通常一个字组为2k个以上的字节)。下表给出了负栅偏置的闪速存储单元在各种情况下各端的电压值。

表2

表2

电路工作原理下面以一种1Mb闪速存储器为例,来说明闪速存储器的擦除和编程。当擦除时,阵列中所有单元的源结都接到12V电压,所有字节都接地,内部擦除确认电路和适当的擦除算法相结合,使擦除阂值小于 ,其擦除算法如图1(a)所示。如果一些字节需要擦除多于1次才能达到希望的擦除阂值

,其擦除算法如图1(a)所示。如果一些字节需要擦除多于1次才能达到希望的擦除阂值 ,那么擦除和验证程序将进行迭代编程算法,如图1(b)所示。当选择栅和漏结接高电位,而源端接地时,热电子由漏结注入到浮栅,内部编程确认电路保证单元的编程阂值大于或等于

,那么擦除和验证程序将进行迭代编程算法,如图1(b)所示。当选择栅和漏结接高电位,而源端接地时,热电子由漏结注入到浮栅,内部编程确认电路保证单元的编程阂值大于或等于 。由于编程发生在漏结,而擦除发生在源结,所以应分别对它们进行优化1。

。由于编程发生在漏结,而擦除发生在源结,所以应分别对它们进行优化1。

图1

图1

闪速存储单元的特点闪速存储器是一类非易失性存储器NVM(Non-Volatile Memory)即使在供电电源关闭后仍能保持片内信息;而诸如DRAM,SRAM这类易失性存储器,当供电电源关闭时片内信息随即丢失。

Flash Memory集其它类非易失性存储器的特点:与EPROM相比较,闪速存储器具有明显的优势—在系统电可擦除和可重复编程,而不需要特殊的高电压(某些第一代闪速存储器也要求高电压来完成擦除和/或编程操作);与 相比较,闪速存储器具有成本低、密度大的特点。其独特的性能使其广泛地运用于各个领域,包括嵌入式系统,如PC及外设、电信交换机、蜂窝电话、网络互联设备、仪器仪表和汽车器件,同时还包括新兴的语音、图像、数据存储类产品,如数字相机、数字录音机和个人数字助理(PDA)2。

相比较,闪速存储器具有成本低、密度大的特点。其独特的性能使其广泛地运用于各个领域,包括嵌入式系统,如PC及外设、电信交换机、蜂窝电话、网络互联设备、仪器仪表和汽车器件,同时还包括新兴的语音、图像、数据存储类产品,如数字相机、数字录音机和个人数字助理(PDA)2。

闪速存储器中的误差校正(ECC)技术在闪速存储器中,用浮栅上电荷的多少来代表逻辑“0”和逻辑“1”。在擦除和编程过程中,由于隧道氧化层中存在高能电子的注入和发射,会带来缺陷和陷阱的产生存储在浮栅上的电子会通过隧道氧化层的缺陷和陷阱泄露。在读出时,由于 加到控制栅,浮栅慢慢地收集电子。电子的泄漏和收集引起了存储晶体管阂值电压的减少或增大,并且可能引起随机位失效。

加到控制栅,浮栅慢慢地收集电子。电子的泄漏和收集引起了存储晶体管阂值电压的减少或增大,并且可能引起随机位失效。

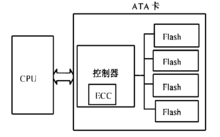

闪速存储器系统必须保证即使在经过 次擦写后存储的数据仍然能保持10年。通常用误差校正技术来提高闪速存储器的可靠性。在ATA卡中,采用闪速控制器,包括ATA接口来处理闪速芯片的读写,如下图所示:

次擦写后存储的数据仍然能保持10年。通常用误差校正技术来提高闪速存储器的可靠性。在ATA卡中,采用闪速控制器,包括ATA接口来处理闪速芯片的读写,如下图所示:

图2

图2

近年来,不带控制器的单闪速芯片的应用市场,如私人数字助理(personal digital assistams, PDA's)、IC卡和数字摄象机等正在扩大,所以需要直接和CPU相连的闪速存储器尽管带ECC的闪速存储器芯片与不带ECC的闪速存储器芯片相比,芯片面积增大10%,但其价格却低。

在闪速存储器中,擦除操作以字组为单位进行,所以除了位出错率外,还引入字组出错率,即在一个字组中出现错误的概率。对于8kb,字组出错率要求小于 。

。

存储单元的比较80年代中期以来,EPROM的容量每两年翻一番。通用 与EPROM相比,具有价格低、擦除简单等优点,但由于每个存储单元有两只晶体管,开发大容量

与EPROM相比,具有价格低、擦除简单等优点,但由于每个存储单元有两只晶体管,开发大容量 是非常困难的。用2μm工艺制作的两管

是非常困难的。用2μm工艺制作的两管 的最大容量为64kb。Masupka等人利用只有1只晶体管的

的最大容量为64kb。Masupka等人利用只有1只晶体管的 单元和新的擦除编程电路技术及高速灵敏度放大器,于1987年报道了第一块256kb闪速

单元和新的擦除编程电路技术及高速灵敏度放大器,于1987年报道了第一块256kb闪速 (即闪速存储器)。之所以称为闪速,是因为它能同时、快速地擦除所有单元。下表比较了第一块闪速存储器与EPROM,一次编程PROM,

(即闪速存储器)。之所以称为闪速,是因为它能同时、快速地擦除所有单元。下表比较了第一块闪速存储器与EPROM,一次编程PROM, 的性能3。

的性能3。

表3

表3

1989年报道了1Mb的闪速存储器,下面是该闪速存储器的主要参数:

表4

表4

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国