基本概念

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑元件有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

计数器计数器功能:统计输入脉冲的个数。

计数器除了直接用于计数外,还可以用于定时器、分频器、程序控制器、信号发生器等多种数字设备中。

按计数器中的触发器是否同时翻转分类:同步计数器、异步计数器。

按计数器中数字的编码方式分类:二进制计数器、非二进制计数器。

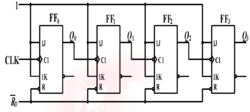

异步计数器电路组成和逻辑功能分析:

二进制加法计数规则:如果低位已经为1,则再记入1时就应回到0,同时向高位送出进位信号。因此,只要将T'触发器从1变加时输出端电位的跳变做为进位信号,并接至高一位触发器的时钟输入端,就可以得到多位二进制加法计数器了。

异步二进制计数器的特点:

(1)异步二进制计数器可由T'触发构成,触发器之间串接低位触发器的输出,作为高位触发器的时钟。

(2)由于触发器的状态翻转是由低位向高位逐级进行的,因此,计数速度较低。

(3)若CLK脉冲的频率为f,则 ~

~ 输出脉冲的频率

输出脉冲的频率 、

、 、

、 、

、 。常称这种计数器为分频器。

。常称这种计数器为分频器。

同步计数器根据计数器的功能要求,n位二进制计数器用n个存储单元电路组成,存储单元的状态表示二进制数,存储单元由触发器实现;输入脉冲将使各位触发器的状态按计数规律变化,即每输入一个脉冲,由触发器的状态表示的二进制数必须加1。

由于是同步计数器,输入脉冲将同步加到各触发器的时钟输入端,因此只有通过控制触发器的驱动信号来达到控制触发器状态的目的。

同步二进制加法计数器的特点:

(1)由n个触发器构成的同步二进制加法计数器的模为 ,没有多余状态,利用率最高;

,没有多余状态,利用率最高;

(2)用T触发器构成的同步二进制加法计数器,其电路结构有两条规则:

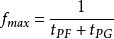

(3)同步计数器工作速度快,这种计数器的最高工作频率可达:

寄存器和移位寄存器寄存器寄存器用途:暂时存放二进制数码。

寄存器作为一个逻辑部件来使用,一般都包含有触发器堆和控制电路两个部分。

移位寄存器功能:存放代码、移位。

移位寄存器组成:移位寄存器中的存储电路可用时钟控制的无空翻的D、RS或JK触发器组成。

触发器触发器为同步操作时序逻辑元件,其输出由输入时钟所规定的时刻的数据输入确定。因此,可将时钟想象为对数据采样的控制,即在由时钟转换所确定的时刻,对数据进行采样。由此可见,触发器应属于时钟驱动元件,这是同步时序电路由时钟实现同步控制的基础。对于触发器的综合有如下规则:

(1)每一个同步赋值的信号对应一个触发器。

(2)如果同步赋值语句中的目标变量在未赋值之前就被使用,则该变量可对应一个触发器;否则,其只是作为中间数据的暂存,不产生硬件元件。

(3)一个同步赋值中的目标变量或目标信号不能在其它赋值语句中被赋值,但是,一个向量的单个元素可以分别处理。

(4)每个进程只允许有一个时钟.

(5)赋值的目标信号与目标变量的综合方法不同:

a.信号的时序赋值可综合为触发;

b.变量的时序赋值,只有当变量在赋值之前读取时才采用触发器;否则,不采用触发器1。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国