基本概念

当前,为了满足通信、多媒体和数字处理等高端应用,片上系统己不仅仅集成一个处理器,而更多的是将多个处理器集成到系统中,甚至还需要结合片外的处理器共同工作。典型的应用是将CPU与DSP (Digital singnal processor)集成到系统中,其中CPU负责系统的复杂控制,DSP负责系统的复杂计算,通过片上系统,集中规划,将两类处理器有机的结合起来,充分发挥各自的优势,完成系统的各项功能。由于系统集成了多个处理器,每个处理器相当于系统的一个主机,各个处理器在与共享资源间通信时,存在一定的逻辑冲突,造成了系统内部通信的一系列问题。

目前主流的多处理器通信方式有以下四类:

(1)共享存储器通信机制;

(2)Mailbox硬件通信机制;

(3)DMA数据搬运通信机制;

(4)串口主从模式通信机制。

多处理器通信机制目前主流的多处理器通信方式有以下四类1。

共享存储器通信机制共享存储器方式比较适合多处理器对于共享存储的处理,其实现方式是设立共享存储状态查询位来进行通信和识别。实现时在一个存储器中放有共享存储器的状态标志,该状态标志类似于信号灯。每次需要访问共享存储的主机设备需先访问该状态标志,如果此时存储器被其他处理器占用则等待其他设备访问结束后再进行访问。这种方法实现简单,需要配置的控制信息也较少。由于对状态标志需要进行识别,因此会增加一定的软件复杂度。

Mailbox硬件通信机制Mailbox作为多处理器系统中处理器间进程同步和数据交换的硬件机制,其优点是应用相对的广,速度快。采用Mailbox的方式,主要是通过传输控制信息的方式进行多处理器通信。根据系统要求,可以定义不同的Mail来实现系统行为。例如:可以定义固定流量的数据传输,也可以定义固定区块的数据传输。通信双方的数据传输,属于片内并行数据传输,因此实时性好,速度快。同时还可以兼容中断和查询模式,减小控制CP U的处理时间压力。如果单纯用于固定的数据传输则Mail设计简单。但如果Mail定义的类型较多,会增加一定的Mail识别难度及识别时间。

DMA数据搬运通信机制DMA (direct memory access)方式能够有效地缩减数据通信对处理器的时间占用,在传送大量数据时能发挥一定的作用。主要使用在程序更新及成片数据搬运方面。DMA可以作为辅助解决多处理器通信的部件。

串口主从模式通信机制串口主从模式主要使用串口通信设备完成,将多个处理器分为主设备与从设备。当主处理器需要数据时就通过DART (Universal asynchronous receiver/ transmitter)向从处理器发送请求数据命令,从处理器通过串口将数据发送去主处理器。由于串口通信延时较大,主处理器必须等待所有的数据从DART传入主处理器区域的SRAM进行组合,或者主处理器自身进行组合后,再处理方可使用,导致通信效率较低。同样从处理器在通信期间也不能向对应的存储区进行数据更新操作。所以传输和处理时间需要重点考虑。

使用串口主从模式进行通信优点在于对软件程序方面的依赖较少,缺点在于对内部电路结构有一定依赖性,传输模式单一,时间久.若设计复杂的通信协议,则对软件编程压力大。

多CPU系统中的数据共享数据共享是指多个CPU之间通过一个或几个存贮器来传递相互间的信息。通常一个CPU将要传递的数据,写入到存贮器的固定区域,然后通知另一个CPU去取出数据,对数据进行处理。将处理的结果再写入到存贮器某一区域,通知有关CPU取走并进行处理。

数据共享是多CPU系统传递信息、协调任务的一种重要手段。通常共享的存贮器可以是双端口RAM,也可以是串口 。在实际中要根据系统的实时性要求进行选择。一般,对于实时性要求高、需要传输大量数据的系统宜选用双端口RAM作为共享存贮器,如音频、视频信号的分析处理,否则宜选用价格相对便宜的串口

。在实际中要根据系统的实时性要求进行选择。一般,对于实时性要求高、需要传输大量数据的系统宜选用双端口RAM作为共享存贮器,如音频、视频信号的分析处理,否则宜选用价格相对便宜的串口 作为共享存贮器(如24C02,93C46等),以优化设计降低成本。

作为共享存贮器(如24C02,93C46等),以优化设计降低成本。

多CPU之间的通信利用双端口RAM实现CPU之间通信双端口RAM是一种高速的存储器芯片,有两套地址总线、数据总线和控制总线,并有一套竞争裁决电路。因此,2个CPU在仲裁电路控制下,可以通过各自的地址总线、数据总线对其进行读写操作,方便地进行CPU之间的数据交换。常用的CMOS双口RAM有IDT7132, ID7102等。利用双端口RAM组成的多CPU系统原理如图所示:

该系统特点是数据交换量大、速度快,适用于快速数据传输,但是系统的成本较高。能否用单端口RAM实现双端口的功能呢,答案是肯定的。

利用单端口RAM实现CPU之间的通信顾名思义,单端口RAM只有一套地址总线、数据总线、控制总线。要实现双端口RAM的功能,就必须由硬件电路将一套总线变成两套总线,分属2个CPU控制。另外还必须设计一套竞争仲裁电路,防止2个CPU同时对RAM的操作冲突。好在这种接口电路的设计并不是太困难,74HC244, 74HC245再加一些门电路就能解决问题。

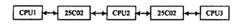

利用串口EPROM实现CPU之间的通信串口 由于其引线少,价格低廉,在嵌入式系统中得到了广泛的应用。下面以共享25C02为例,介绍多CPU之间的数据传输。原理如图所示:

由于其引线少,价格低廉,在嵌入式系统中得到了广泛的应用。下面以共享25C02为例,介绍多CPU之间的数据传输。原理如图所示:

图中CPU1与CPU2通过共享25C02,CPU2与CPU3通过共享25C02完成他们之间的通信。

利用串行总线实现多CPU之间的通信随着计算机技术的发展,计算机的串口通信越来越多样化。同步串口通信、异步串口通信、 总线、SPI总线、USB等,由于其实用性好,越来越为设计者所关注。特别是在多CPU嵌入式系统中,各个CPU通过串行总线相连可以方便地进行多CPU之间的通信。

总线、SPI总线、USB等,由于其实用性好,越来越为设计者所关注。特别是在多CPU嵌入式系统中,各个CPU通过串行总线相连可以方便地进行多CPU之间的通信。

(1)用 总线实现多CPU之间的通信

总线实现多CPU之间的通信

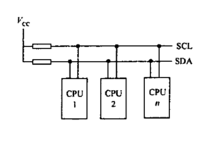

(Inter Intergrated Circuit)总线是由Philips公司提出并注册的一种总线接口标准,是一种主从结构的二线同步总线,其中一根是同步移位时钟SCL,另一根为数据线SDA。各CPU通过2条线相连,其原理如图所示:

(Inter Intergrated Circuit)总线是由Philips公司提出并注册的一种总线接口标准,是一种主从结构的二线同步总线,其中一根是同步移位时钟SCL,另一根为数据线SDA。各CPU通过2条线相连,其原理如图所示:

系统中的CPU可以选用带有 总线接口的,如Philips公司的80C652, P87LC764等,其通信软件包可以在网上下载,对于不带

总线接口的,如Philips公司的80C652, P87LC764等,其通信软件包可以在网上下载,对于不带 总线接口的CPU,可以通过I/O模拟Iz C总线,相应软件可从网上下载,也可自己编写。

总线接口的CPU,可以通过I/O模拟Iz C总线,相应软件可从网上下载,也可自己编写。

有4种工作模式、主发送模式、主接收模式、从发送模式、从接收模式。根据各子系统需要,合理选用其工作模式即构成 总线多CPU通信系统。Iz C总线的数据传送格式如图所示:

总线多CPU通信系统。Iz C总线的数据传送格式如图所示:

S为Start信号,SLA为从机地址,也可以是通信地址;R/W为读写控制位;A为ACK应答位;DATA0~DATA7为数据字节;S/P为下一个start或stop信号。

(2)利用SPl总线实现多CPU之间通信

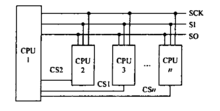

SPI( Serial Peripheral Interface)总线是由Motorola公司提出并拥有商标的一种总线接口标准,是一种4线同步串行总线。4根线分别是:片选CS;串行移位SCK;串行移位数据输入SI;串行移位输出SO。在同一时刻串行数据移位输入、输出不能同时进行,因此,可以将二者连在一起,共用一根口线(即三线同步串行并线)。

如图是典型的基于 SPI总线组成的多CPU系统:

系统中的CPU可以采用带有SPI总线接口的单片机。对于没有SPI总线接口的单片机系统,可使用普通I/O口模拟SPI总线,其通信程序自编。利用SPI总线组成的一个三级多CPU系统运行结果良好。利用串行总线实现多CPU通信,其优点是:连线简单、方便、可靠,产品性价比好;缺点是数据传输速度慢,实时性差,不宜用于数据量大、通信频繁的多CPU系统2。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国