基本概念

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。PU、MCU及DSP等电子器件中的加法运算是最基础、最常见的运算方法,常见加法器是位并行的,在一个时钟周期内完成加法运算。由于传统加法器位数有限,所以传统计算机能运算的数值范围是有限的,能精确到的浮点数位数是有限的。如果将传统加法器设计为位串行行操作,利用多个时钟周期完成一次加法运算,即输入操作数和输出结果由并行输入/输出改为随时钟串行输入/输出,比如由低到高串行输入0101和1001到位串行加法器,输出结果就是1110由低位到高位输出的数字波形,则其运算结果就可以存入FIFO或RAM 中,这样不仅能够提高加法器处理数值的上限,而且也能减少硬件资源的应用。

串行二进制加法器即加法器执行位串行行操作,利用多个时钟周期完成一次加法运算,即输入操作数和输出结果方式为随时钟串行输入/输出。位并行加法器速度高,但是占用资源多。在许多实际应用中并不需要这样高的速度,而是希望减少硬件资源占用率,这时就可以使用串行二进制加法器。

串行二进制加法器设计1位串行加法器二进制数的加法过程是从最低位开始的,低位决定进位数:1和1相加就进1,其他进位0。下一位操作数与上一位进位决定本位相加结果:进位和操作数中1的个数不大于1则进位为0,否则进位为1。

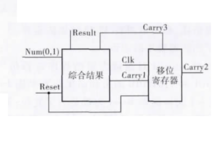

图1

图1

位串行加法器采用输入时钟Clk来控制加法器的操作,其逻辑如图1所示,输入信号Num(0,1)代表两个加法操作数Num(0) 和Num(1);Reset是复位端,低电平时复位;Clk 是同步时钟;Carry1、Carry2和Carry3是Num(0) 和Num(1)对应位相加的进位结果。要完成整个加法操作,主要是进位和本位操作数相加,而进位结果是由低位决定的。所以本位运算结果输出后,必须保留进位到下两位操作数到来,这样操作数才能实现和上一位进位结果一起运算。由于最低位没有进位,它的处理方式稍有特殊:在上电复位后Carry3为0,所以可以用该时刻的0作为最开始两位操作数的进位,具体操作步骤如下:

a.Num(0) 和Num(1) 的求和结果与进位结果,通过组合逻辑电路分别输出到Result 端和Carry1。

b.Clk上升沿到来后Carry1才赋值给Carry2,Carry2 移位至Carry3;Clk下降沿到来时,重复上次移位操作,此时Carry3就是第一位操作数的进位。

c.操作数第二位输入与Carry3求和,回到步骤a。依此循环,直到结果输出完毕1。

2位串行加法器在数字串行加法器中,字长为W的操作数被分为P个位宽为N(N能被W整除,P=W/N)的数字,然后从低位开始相加,在P个时钟内完成加法操作。P个时钟周期称为一个采样周期(Sample Period)。

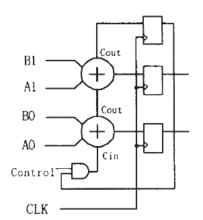

2位串行加法器,即N=2的串行加法器结构如图所示:

如果输入操作数的字长为8,那么串行加法器可以在4个时钟周期内完成加法运算。这个加法器只用了两个全加器的资源,比一般的8bit行波进位加法器小。

数字串行加法器的控制也比较简单,输入移位寄存器完成并行-串行转换功能。通过移位操作不断为加法器提供位宽为N的操作数;control信号指示了新采样周期的开始,此时carry清零;输出移位寄存器完成串行-并行转换,输出计算结果。

对于特定的输入字长,通过选择不同的N,可以实现速度、面积不同的数字串行加法器。这样,设计者可以根据实际情况加以选择,提高了设计的灵活性2。

串行进位加法器和超前进位加法器实现多为二进制数相加的电路,称为加法器。根据进位方式不同,有串行进位加法器和超前进位加法器之分。

(1)串行加法进位从最低位进到最高位,即整个进位是分若干步骤进行的。优点是电路结构简单,缺点是运算速度慢。

(2)超前进位的所有位数进位是同时完成的,一个CP脉冲就能完成整个进位过程。优点是运算速度快,缺点是电路复杂。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国