基本概念

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑电路有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

时序逻辑电路时序逻辑是Verilog HDL设计中另一类重要应用。从电路特征上看来,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。电路里面有存储元件(各类触发器,在FPGA芯片结构中只有D触发器)用于记忆信息。从电路行为上讲,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

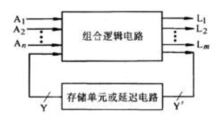

时序逻辑电路由组合逻辑电路和存储电路这两部分组成,其中存储电路由各类触发器(JK触发器、D触发器以及T触发器等类型)构成,并将组合逻辑的部分输出反馈到输入逻辑的输入端口。

结构图如图:

时序电路可通过表达式(电路输出端的输出逻辑表达式、存储电路触发器输出端的驱动或激励表达式,以及表示触发器状态的状态方程)、状态转移表、状态转移图、时序图以及HDL行为描述语言等来描述。若将输入变量和各级触发器状态的全部组合列出,分别代入各级触发器的状态方程和电路的输出方程,则可以计算出各级触发器的次态值和当前输出值,把相应的计算结果列成真值表就可得到状态转移表。

分类时序逻辑电路可分为同步时序电路和异步时序电路两大类。

同步时序逻辑电路在同步时序逻辑电路中,存储电路内所有触发器的时钟输入端都接于同一个时钟脉冲源,因而,所有触发器的状态(即时序逻辑电路的状态)的变化都与所加的时钟脉冲信号同步。

异步时序逻辑电路在异步时序逻辑电路中,没有统一的时钟脉冲,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化才与时钟脉冲同步,而其他触发器状态的变化并不与时钟脉冲同步。

故障分析带有时序逻辑电路的数字电路主要故障分析:

(1)时钟:时钟是整个系统的同步信号,当时钟出现故障时会带来整体的功能故障。时钟脉冲丢失会导致系统数据总线、地址总线或控制总线没有动作。时钟脉冲的速率、振幅、宽度、形状及相位发生变化均可能引发故障。

(2)复位:含有微处理器(MPU)的设备,即使是最小系统,一般都具有复位功能。复位脉冲在系统上电时加载到MPU上,或在特定情况下使程序回到最初状态(例如,看门狗Watchdog程序)。当复位脉冲不能发生、信号过窄、信号幅度不对、转换中有干扰或转换太慢时,程序就可能在错误的地址启动,导致程序混乱。

(3)总线:总线传递指令系列和控制事件,一般有地址总线、数据总线和控制总线。当总线即使只有一位发生错误时,也会严重影响系统功能,出现错误寻址、错误数据或错误操作等。总线错误可能发生在总线驱动器中,也可能发生在接收数据位的其它元件中。

(4)中断:带微处理器(MPU)的系统一般都能够响应中断信号或设备请求,产生控制逻辑,以暂时中断程序执行,转到特殊程序,为中断设备服务,然后自动回到主程序。中断错误主要是中断线路粘附(此时系统操作非常

(5)信号衰减和畸变:长的并行总线和控制线可能会发生交互串扰和传输线故障,表现为相邻的信号线出现尖峰脉冲(交互串扰),或驱动线上形成减幅振荡(相当于逻辑电平的多次转换),从而可能加入错误数据或控制信号。发生信号衰减的可能原因比较多,常见的有高湿度环境、长的传输线、高速率转换等。而大的电子干扰源会产生电磁干扰(EMI),导致信号畸变,引起电路的功能紊乱。

应用时序逻辑电路是一种重要的数字逻辑电路,其特点是电路任何一个时刻的输出状态不仅取决于当时的输入信号,而且与电路的原状态有关,具有记忆功能。构成组合逻辑电路的基本单元是逻辑门,而构成时序逻辑电路的基本单元是触发器。时序逻辑电路在实际中的应用很广泛,数字钟、交通灯、计算机、电梯的控制盘、门铃和防盗报警系统中都能见到。

集成计数器的识别与应用计数器在计算机及各种数字仪表中应用广泛,具有记忆输入脉冲个数的功能,还可以实现分频、定时等。计数器种类繁多,按技术体制可分为二进制计数器和N进制计数器;按增减趋势可分为加计数器和减计数器;按技术脉冲引入方式可分为同步计数器和异步计数器。同步计数器的特点是构成计数器的所有触发器共用同一个时钟脉冲,触发器的状态同时更新,计数速度快;而异步计数的特点是构成计数器的触发器不共用同一个时钟脉冲,所有触发器更新状态的时刻不一致,计数速度相对较慢。 在实际应用中,计数器是以集成电路形式存在的,主要有集成二进制计数器、集成十进制计数器两大类,其他进制计数器可由它们通过外电路设计来实现。在每一大类计数器中,又以同步与异步、加计数与可逆计数来细分。

集成寄存器的识别与应用寄存器具有接收数码、存放或传递数码的功能,由触发器和逻辑门组成。其中,触发器用来存放二进制数,逻辑门用来控制二进制数的接收、传送和输出。由于一个触发器只能存放1位二进制数,因此,存放n位二进制数的n位寄存器,需要n个触发器来组成。寄存器有数码寄存器和移位寄存器2种。输入输出方式有并入-并出、并入-串出、串入-并出、串入-串出4种。当寄存器的每一位数码由一个时钟脉冲控制同时接收或输出时,称为并入或并出。而每个时钟脉冲只控制寄存器按顺序逐位移入或移出数码时,称为串入或串出。移位寄存器除了具有存储数码的功能以外,还具有移位功能。所谓移位功能,是指寄存器里存储的数码能在时钟脉冲作用下依次左移或右移。因此,移位寄存器不仅可以用来寄存数码,而且可以用来实现数码的串行-并行转换。

时序逻辑电路的分析时序逻辑电路分析的一般步骤可归纳为:写方程式、求状态方程、进行计算、画状态转换图(或状态转换表)、确定电路的逻辑功能等。

(1)写方程式 仔细观察、分析时序电路,然后再逐一写出以下3个方程。

① 时钟方程:各个触发器时钟信号的逻辑表达式。

② 输出方程:时序电路各个输出信号的逻辑表达式。

③ 驱动方程:各个触发器输入端信号的逻辑表达式。

(2)求状态方程

把驱动方程代入相应触发器的特性方程,即可求出时序电路的状态方程。

(3)进行计算

把电路输入和现态的各种可能取值,代入状态方程和输出方程进行计算,求出相应的次态和输出。

(4)画状态转换图

(5)确定电路的逻辑功能 根据状态转换图确定电路的逻辑功能,必要的话,可用文字详细描述1。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国