数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

特点在组合逻辑电路中,任意时刻的输出值只与当时的输入值有关,即输出惟一地由当时的输入值决定,这是组合电路在逻辑功能上的共同特点。从组合电路的逻辑功能不难想到,既然其输出与电路的历史状况无关,那么电路中就不能包含记忆(存储)单元。这是组合电路在电路结构上的共同特点。

对于组合逻辑电路,其逻辑函数如下:

其中, 为输入变量,

为输入变量, 为输出变量。1

为输出变量。1

电路设计对于一个逻辑表达公式或逻辑电路,其真值表可以是惟一的,但其对应的逻辑电路或逻辑表达式可能有多种实现形式,所以,一个特定的逻辑问题,其对应的真值表是惟一的,但实现它的逻辑电路是多种多样的。在实际设计工作中,如果由于某些原因无法获得某些门电路,可以通过变换逻辑表达式变电路,从而能使用其他器件来代替该器件。同时,为了使逻辑电路的设计更简洁,通过各方法对逻辑表达式进行化简是必要的。组合电路可用一组逻辑表达式来描述。设计组合电路直就是实现逻辑表达式。要求在满足逻辑功能和技术要求基础上,力求使电路简单、经济、可靠、实现组合逻辑函数的途径是多种多样的,可采用基本门电路,也可采用中、大规模集成电路。其一般设计步骤为:分析设计要求,列真值表;然后,进行逻辑和必要变换,得出所需要的最简逻辑表达式;画逻辑图。2

电路分析在asic设计和pld设计中组合逻辑电路设计的最简化是很重要的,在设计时常要求用最少的逻辑门或导线实现。在asic设计和pld设计中需要处理大量的约束项,值为1或0的项却是有限的,提出组合逻辑电路设计的一种新方法。

与逻辑表示只有在决定事物结果的全部条件具备时,结果才发生。输出变量为1的某个组合的所有因子的与表示输出变量为1的这个组合出现、所有输出变量为0的组合均不出现,因而可以表示输出变量为1的这个组合。 组合逻辑电路的分析分以下几个步骤:

(1)有给定的逻辑电路图,写出输出端的逻辑表达式;

(2)列出真值表;

(3)通过真值表概括出逻辑功能,看原电路是不是最理想,若不是,则对其进行改进。

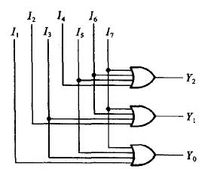

常见组合电路编码器在数字系统中,为了区分一系列不同的事物,将其中的每个事物用一 个二值代码表示,这就是编码的含意。在二值逻辑电路中,信号都是以高、低电平的形式给出的。因此,编码器(Encoder)的逻辑功能就是将输人的每一个高、低电平信号编成一个对应的二进制代码。

个二值代码表示,这就是编码的含意。在二值逻辑电路中,信号都是以高、低电平的形式给出的。因此,编码器(Encoder)的逻辑功能就是将输人的每一个高、低电平信号编成一个对应的二进制代码。

目前经常使用的编码器有普通编码器和优先编码器两类。在普通编码器中,任何时刻只允许输人一个编码信号,否则输出将发生混乱。

在优先编码器(priorityencoder)电路中,允许同时输人两个以上的编码信

号。不过在设计优先编码器时已经将所有的输人信号按优先顺序排了队,当几个输人信号同时出现时,只对其中优先权最高的一个进行编码。1

译码器译码器(Decoder)的逻辑功能是将每个输人的二进制代码译成对应的输出高、低电平信号或另外一个代码。因此,译码是编码的反操作。常用的译码器电路有二进制译码器、二一十进制译码器和显示译码器三类。1

数据选择器数据选择器 它就是从多个输入端中选择一路输出,它相当于一个多路开关。常用的有二选一,四选一,八选一和十六选一,若需更多则由上述扩展。1

加法器实现多位二进制数相加的电路称为加法器。根据进位方式不同,有串行进位加法器和超前进位加法器两种。

本词条内容贡献者为:

李勇 - 副教授 - 西南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国